Method for improving frequency characteristic of common-source operational amplifier

A source terminal and gate technology, which is applied in the direction of improving amplifiers to improve efficiency, differential amplifiers, DC coupled DC amplifiers, etc., can solve the problems of reducing the frequency response characteristics of common source operational amplifiers, so as to improve frequency response characteristics and reduce Effect of Small Parasitic Overlap Capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

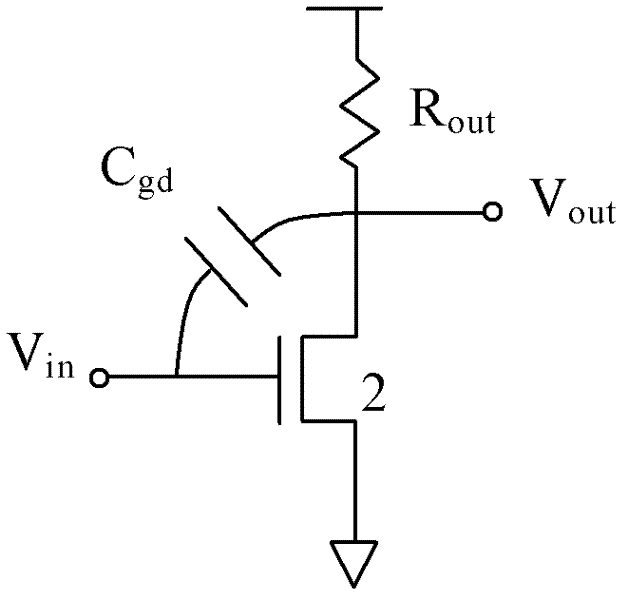

[0027] The following will combine Figure 3A-Figure 4C The above-mentioned spirit and essence of the present invention are described in detail.

[0028] Figures 3A-3C Three steps in the process of fabricating an NMOS device in a common-source operational amplifier in the prior art are exemplarily shown.

[0029] Figure 3A A cross-sectional view of an NMOS device after sidewall deposition in the prior art is exemplarily shown. Such as Figure 3A As shown in , in the manufacturing process of NMOS devices in the prior art, in the first step, LDD (Lightly Doped Drain) structures 11 and 12, STI (Shallow Trench Isolation) structure 13 are first formed under the upper surface of the substrate 10 and 14 , and a gate 15 is formed above the upper surface of the substrate 10 . The LDD structures 11 and 12 are located on both sides below the gate 15 respectively, and are used to form a source terminal and a drain terminal and form an NMOS device together with the gate 15 . The STI...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More