Source-drain lightly-doping method, semiconductor device and manufacturing method thereof

A technology of lightly doped and lightly doped regions, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of no substantial effect of reducing parasitic capacitance, simple steps, etc., to improve the frequency response characteristics, the effect of reducing Miller capacitance, and reducing parasitic overlap capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

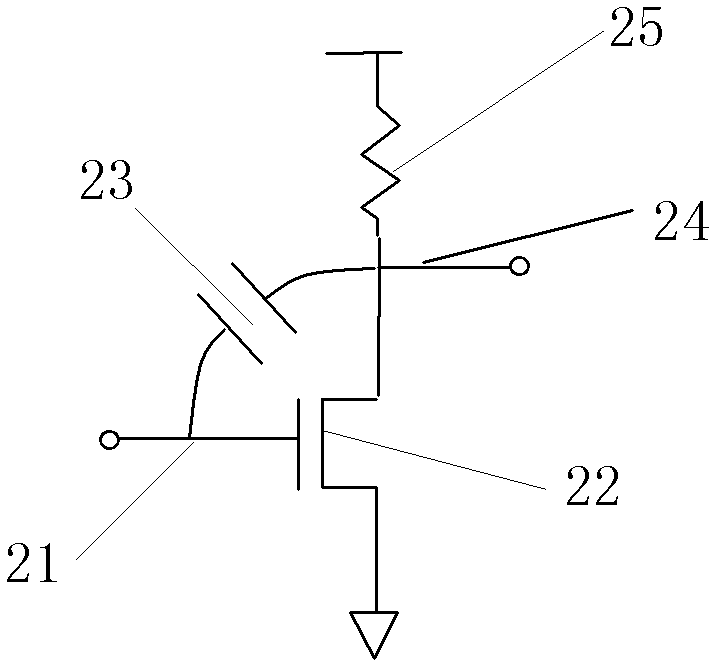

[0022] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0023] In the source-drain light doping method provided by the embodiment of the present invention, the ion implantation direction of the source-drain light doping method is inclined to the source direction and forms an included angle with the direction perpendicular to the substrate. The present invention takes the preparation of NMOS transistors in CMOS device technology as an example.

[0024] Please refer to Figure 4A , first forming a gate structure 44 on a substrate 41, wherein the substrate includes a source region and a drain region;

[0025] Please refer to Figure 4B , with the gate structure 44 as a mask, the source region and the drain region in the substrate 41 on both sides of the gate structure 44 are lightly doped to...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Angle | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More