Dynamic random access memory (DRAM) and method for improving DRAM data access bandwidth

A memory and data technology, applied in the direction of electrical digital data processing, instruments, memory address/allocation/relocation, etc., can solve the problems of increasing the difficulty of interface design, logic resource usage area, IC cost increase, IC area increase, etc. , to achieve the effect of improving access bandwidth, increasing interface data bit width, and avoiding bandwidth occupation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] The present invention will be described in detail below in conjunction with specific embodiments shown in the accompanying drawings. However, these embodiments do not limit the present invention, and any structural, method, or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

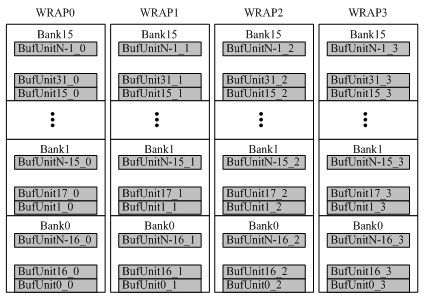

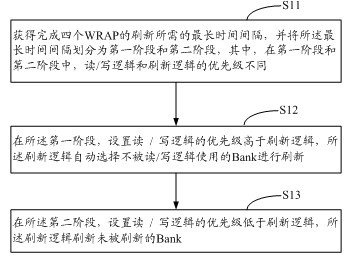

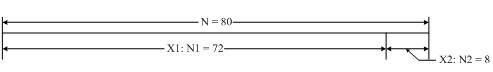

[0048] The present invention adopts two aspects of innovative design to meet the requirements of improving the interface access bandwidth: one is to optimize the DRAM refresh logic to minimize the access bandwidth occupied by the refresh operation; the other is to use multi-stage pipelines to process the high-speed characteristics and large capacity of DRAM DRAM is physically divided into multiple Banks (storage blocks) to achieve high-speed memory that can be accessed randomly. The design scheme of the present invention will be explained below with a memory design example of data packets in the design...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More