Embedded digital ip strip chip

A technology for configuring logic and regions, applied in the field of integrated circuits and designing integrated circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0016] An integrated circuit having a digital strip area is provided. It will be apparent, however, to one skilled in the art that the present invention may be practiced without some or all of these specific details. In other instances, well known process operations have not been described in detail in order not to unnecessarily obscure the present invention.

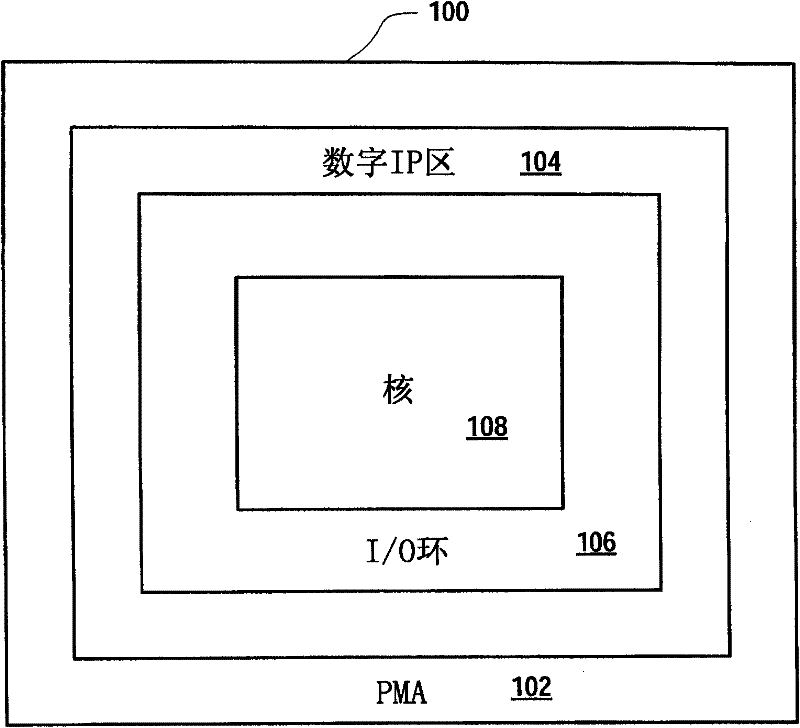

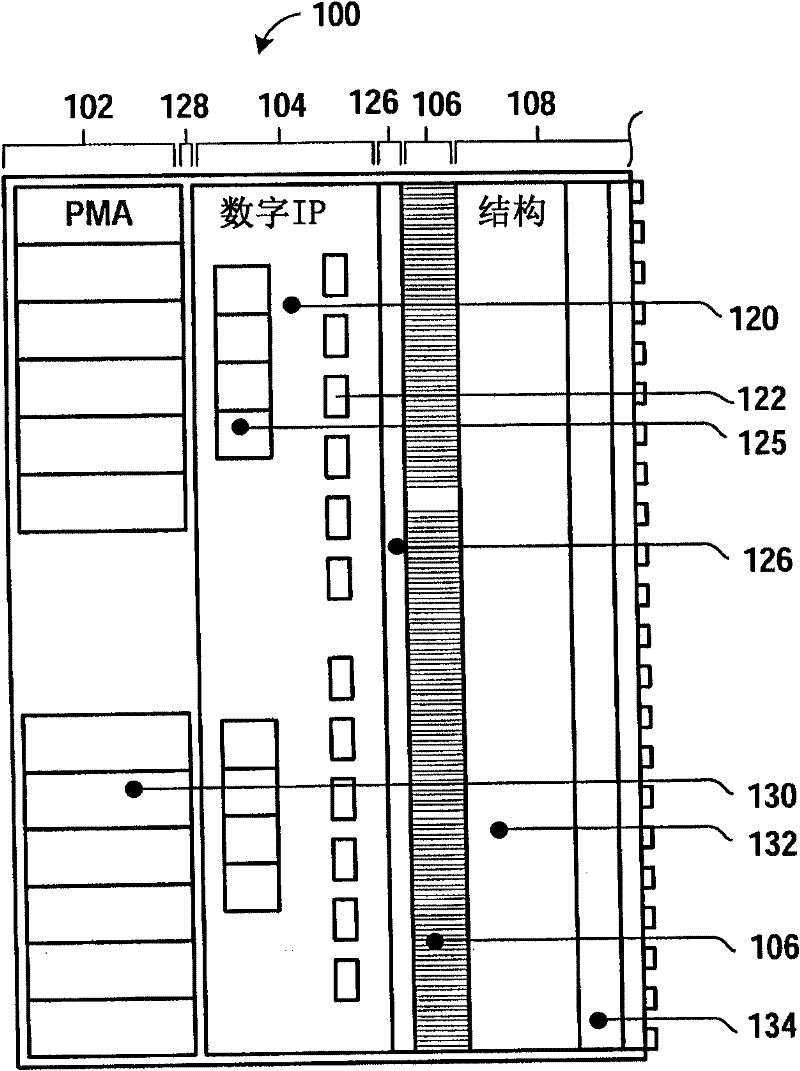

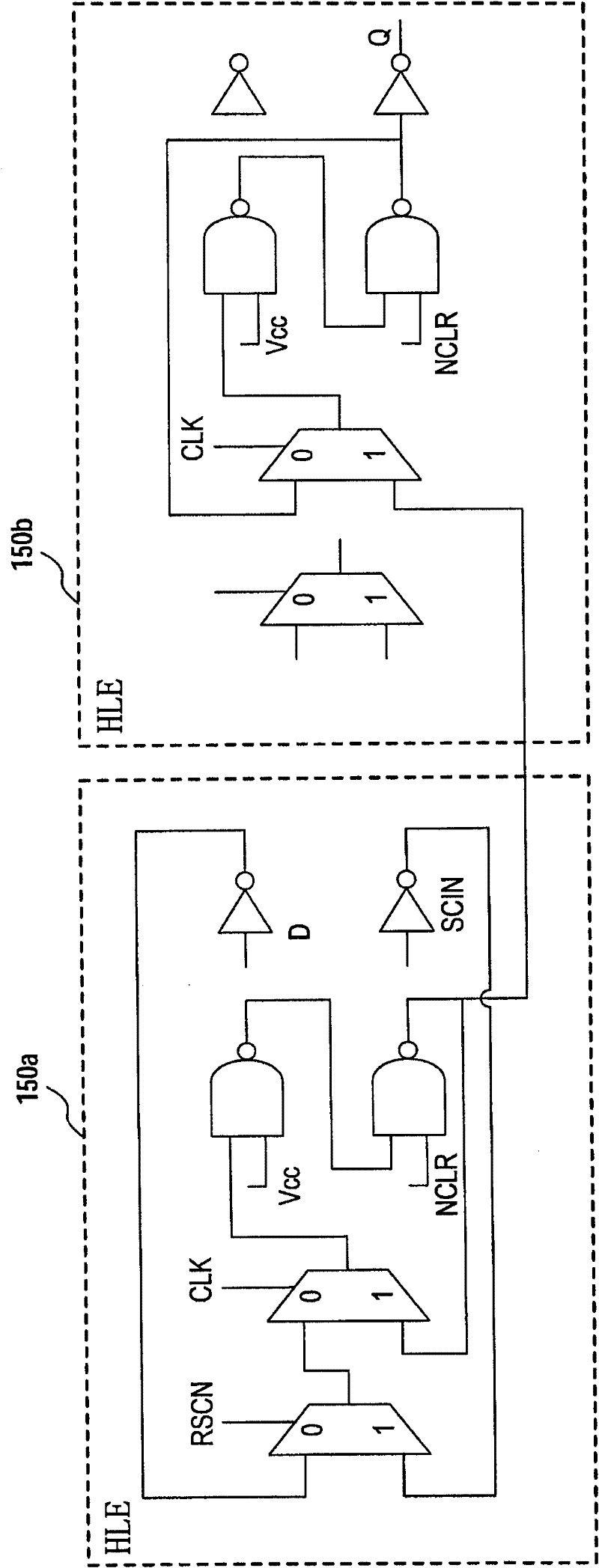

[0017] Embodiments described herein provide integrated circuits with mixed platforms. In one embodiment, an integrated circuit has a programmable logic device (PLD) core region (such as a field programmable gate array FPGA core region) and a strip or block of digital intellectual property (IP), which may also be referred to as are structured application specific integrated circuit (ASIC) strips or arrays. The digital strip includes base cells whose digital functionality can be modified by a limited number of metal masks, and standard cell macros that accommodate mature functions / protocols. In one embodiment, the digi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More