Batch testing method for complex programmable logic device

A technology of programming logic and batch testing, applied in circuit breaker testing, electronic circuit testing, instruments, etc., to save testing time, improve testing efficiency, and reduce testing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

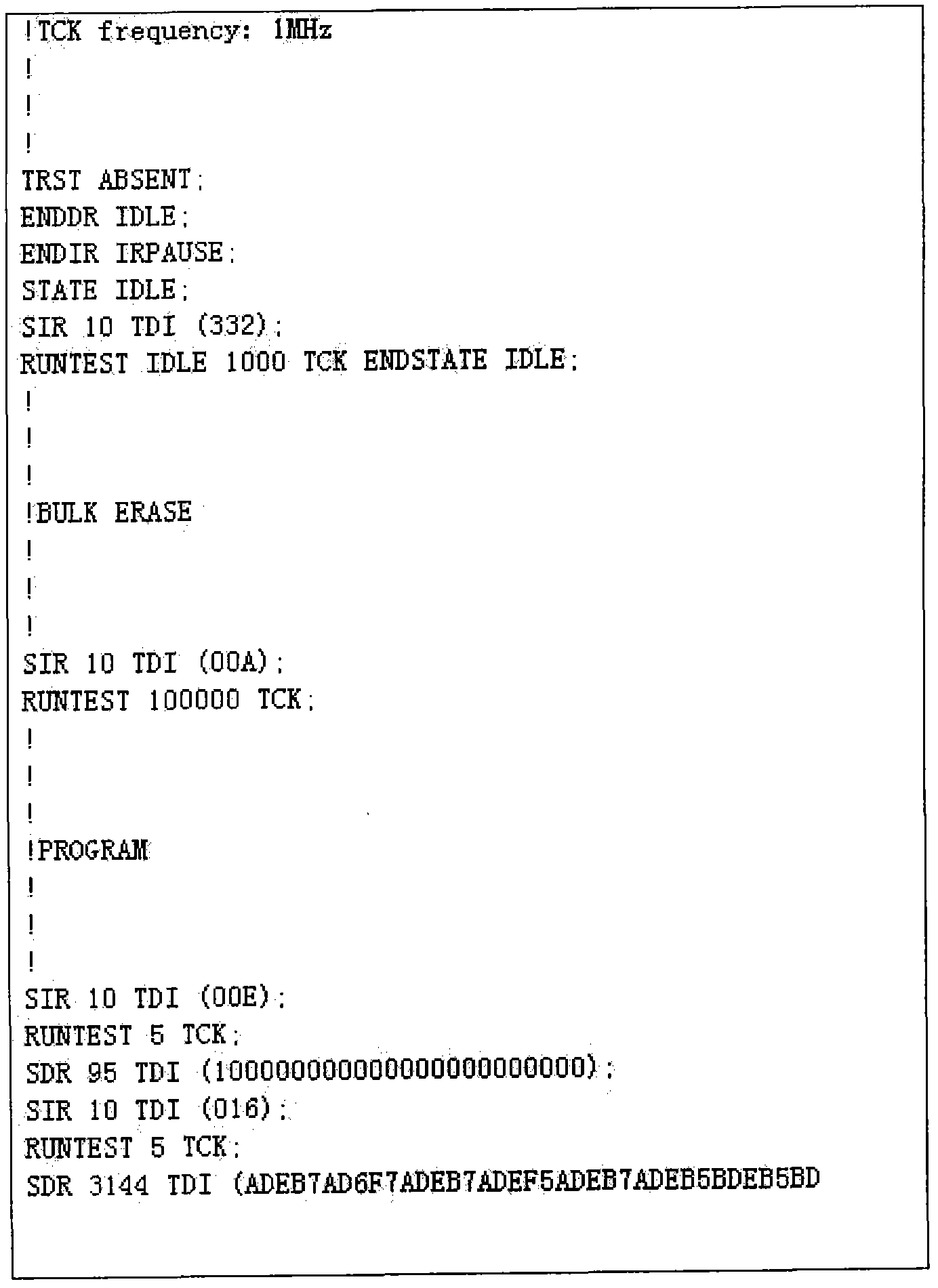

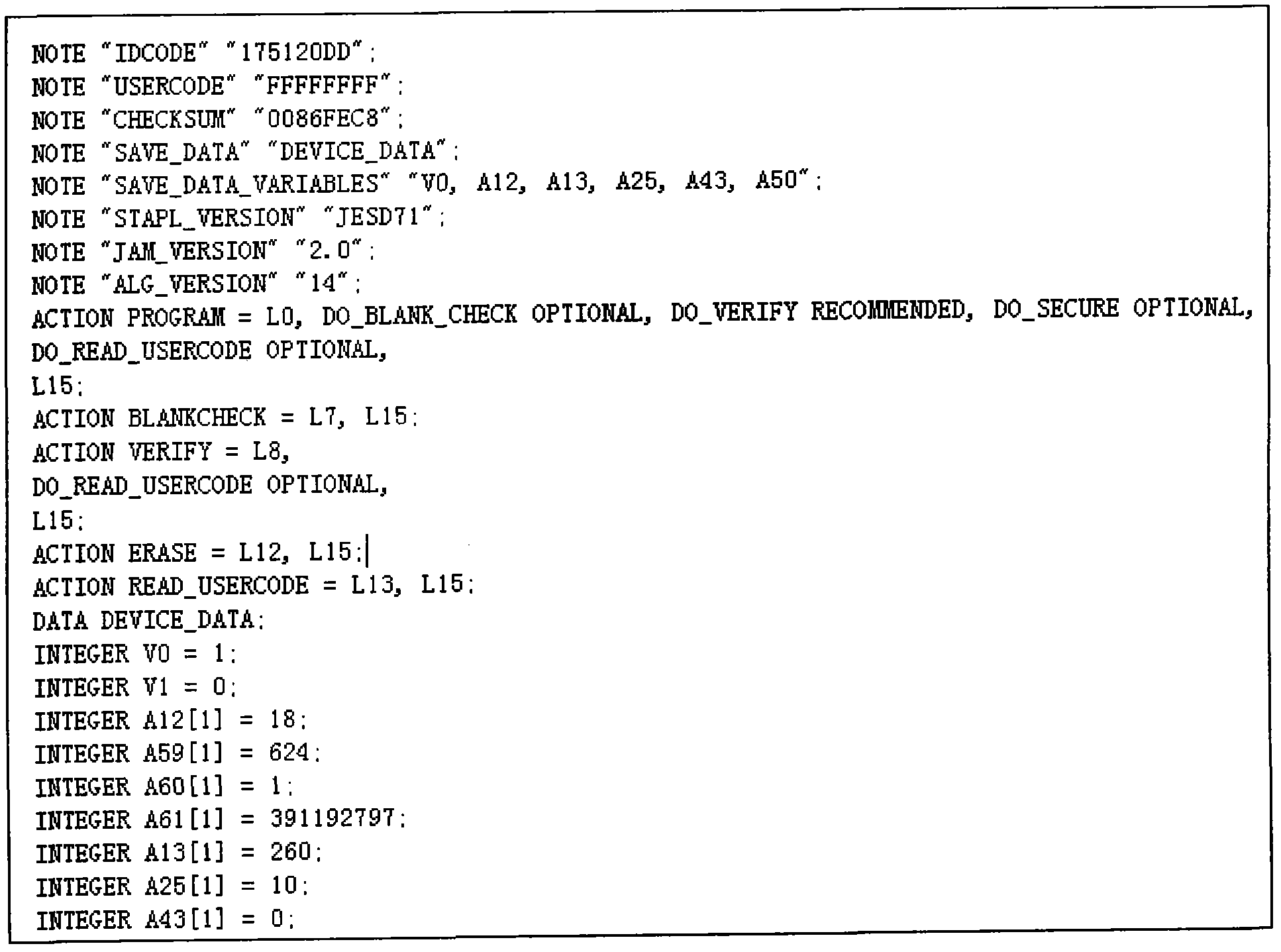

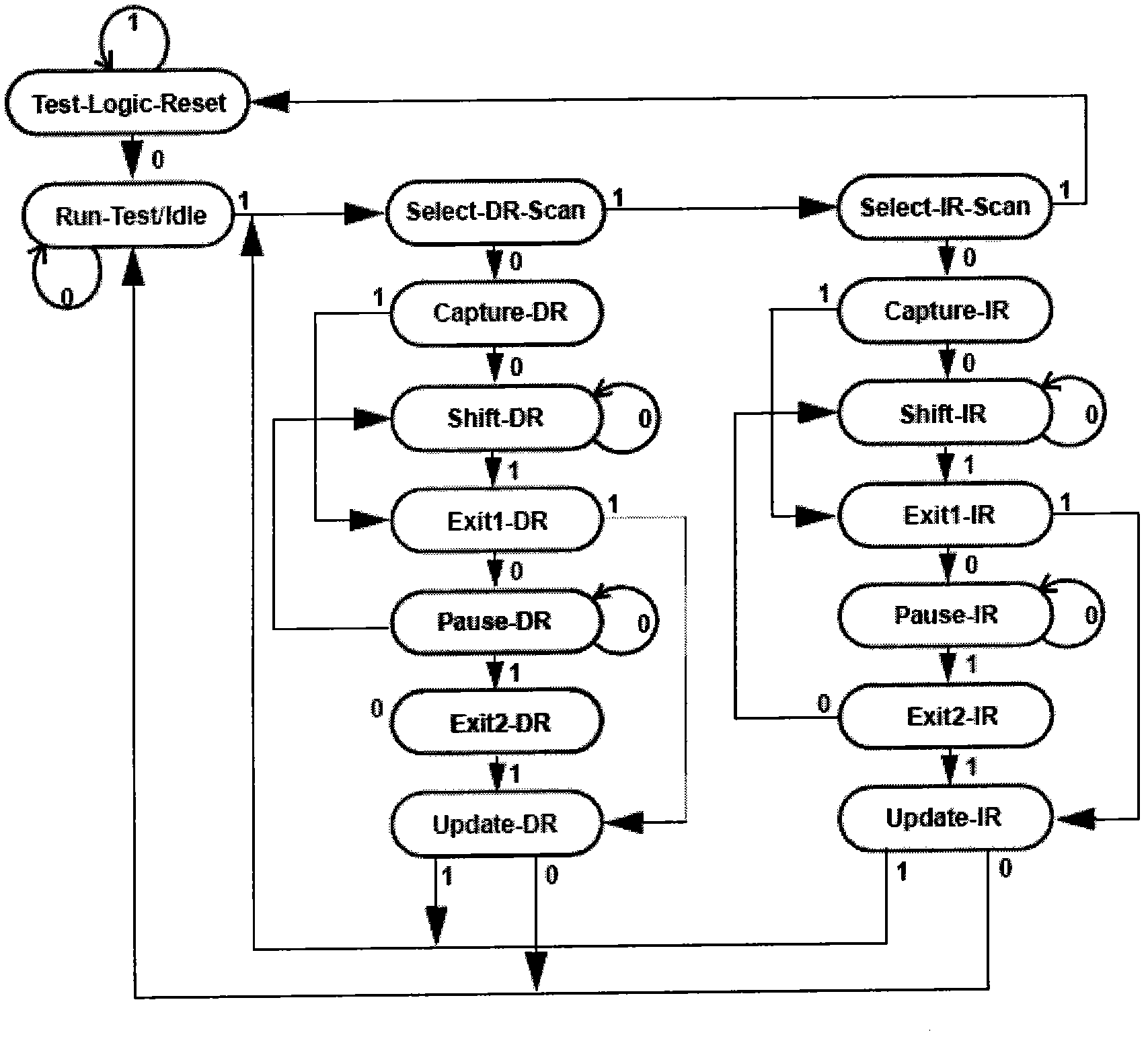

[0043] The basic train of thought of the CPLD batch test method provided by the present invention is: at first obtain the programming file of CPLD and the test emulation file with EDA tool software according to fault model, the programming file of CPLD is changed and decomposed and converted into ATE recognizable programming vector, will The corresponding test simulation files are converted into test vectors recognizable by ATE, and all vectors are loaded to the automatic test equipment at one time, and online programming and testing for multiple fault models of CPLD are realized on ATE. During the test process, each CPLD under test is only connected to ATE Once, the operation time is saved, and the test efficiency is improved through the parallel test technology, and the mass production test of CPLD is realized.

[0044] In order to realize the above-mentioned technical ideas, it is the first choice to adopt mid-to-high-end integrated circuit automatic test equipment (abbrevia...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More