Semiconductor structure and making method thereof

A manufacturing method and semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of large cross-sectional area of the second contact hole, unfavorable area saving, etc., to achieve the benefit of process design, The effect of saving area and reducing the process window

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

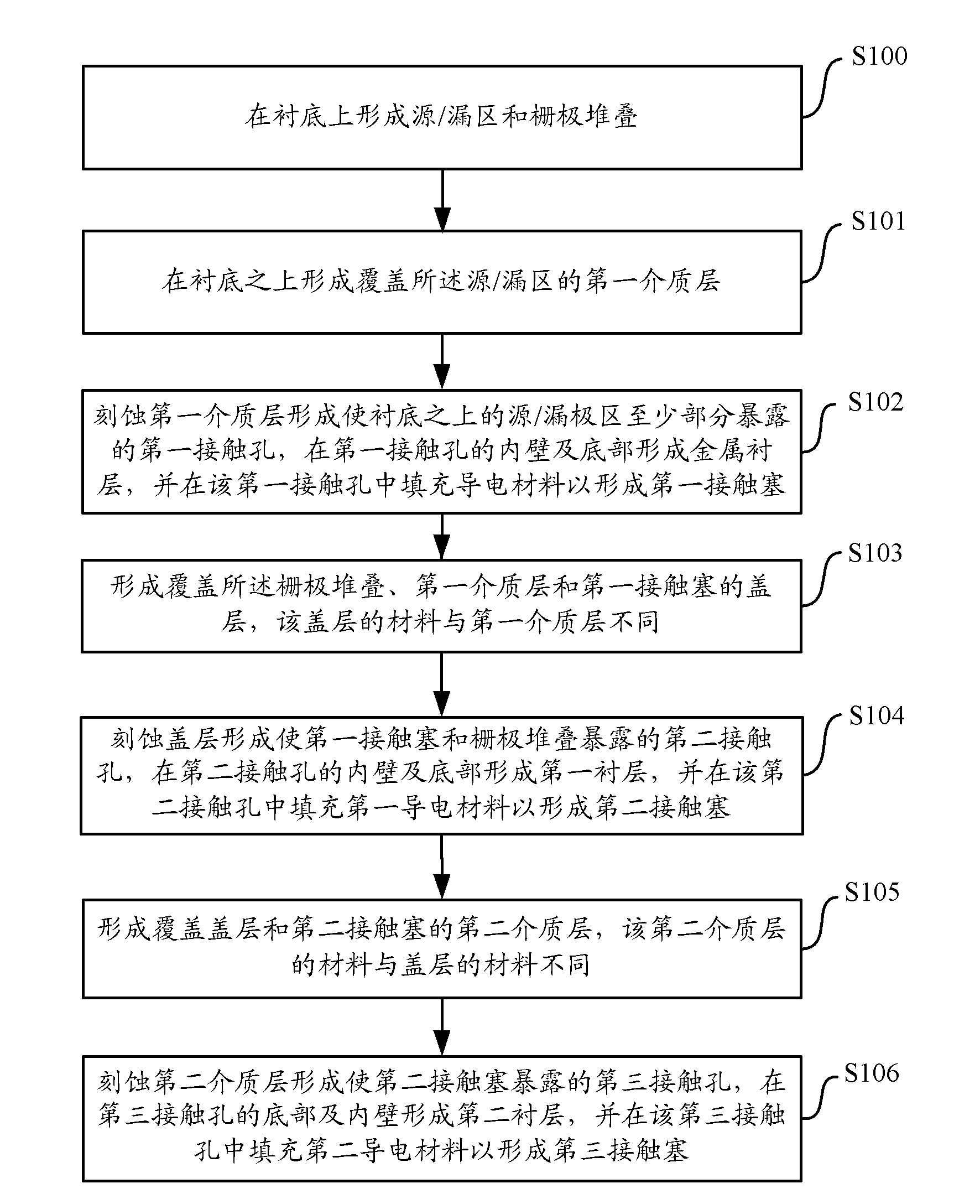

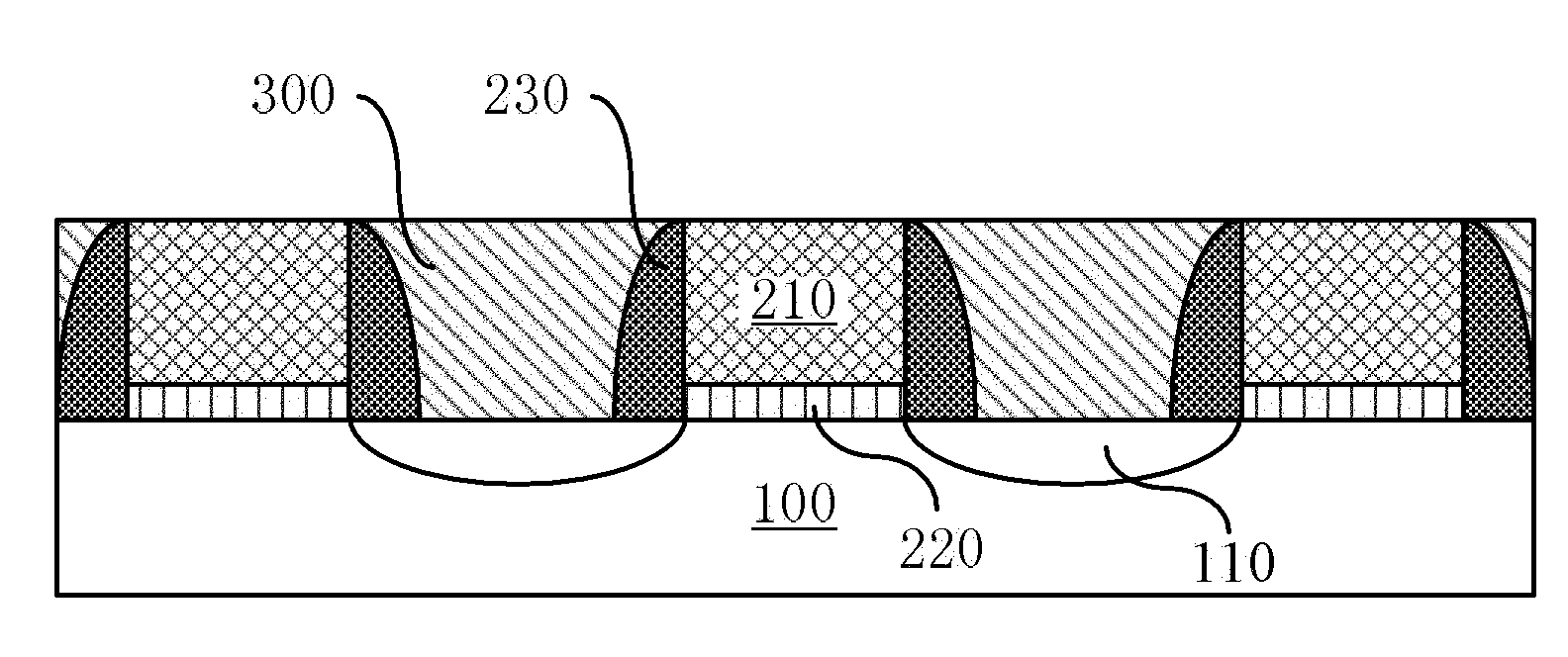

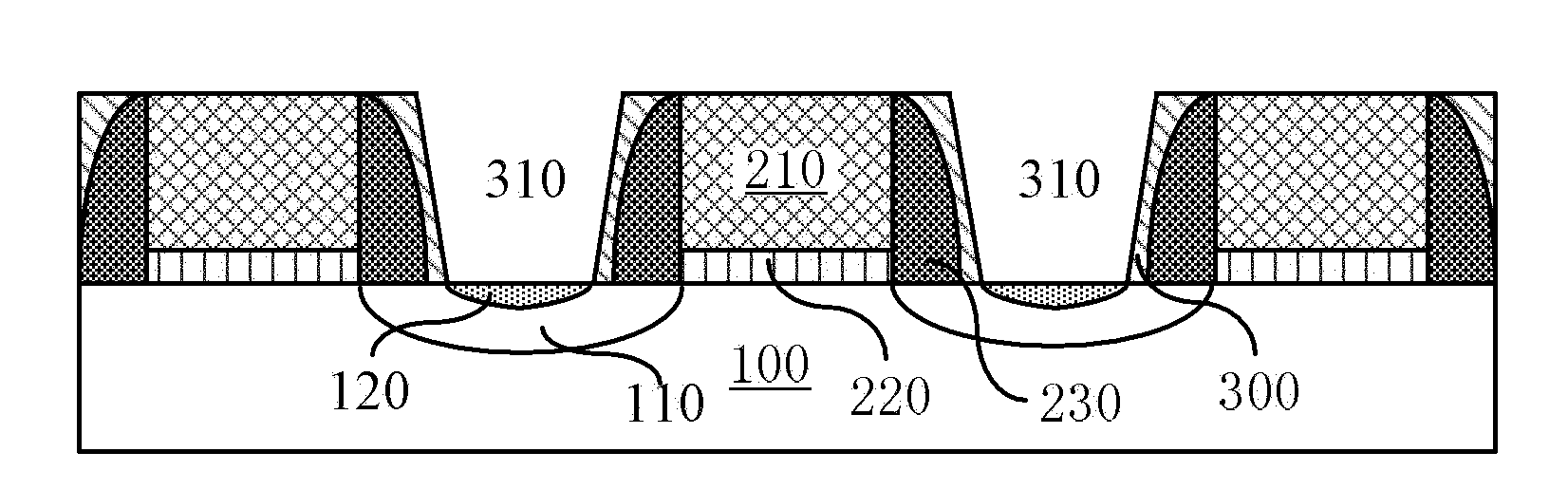

[0060] Please refer to Figure 10 to Figure 12 . The semiconductor structure includes a substrate 100, a gate stack, a spacer 230 (this document only explicitly shows an example of a semiconductor structure including a sidewall 230, but in other embodiments, the sidewall 230 may not be included), a first dielectric layer 300 , the first contact plug 320, the cover layer 400, the second contact plug 420, the second dielectric layer 500, the third contact plug 520 and each lining layer (such as the metal lining layer, the first lining layer and the second lining layer, the figure is not shown), wherein the source / drain region 110 is formed in the substrate 100; the gate stack is formed on the substrate 100, and the sidewall 230 is formed at the sidewall of the gate stack; the first dielectric layer 300 covers the source / drain region 110, the cover layer 400 covers the gate stack and the first dielectric layer 300, the first contact plug 320 penetrating through the first dielect...

Embodiment 2

[0069] On the basis of the description of the same part in the reference embodiment one, refer to Figure 16 to Figure 20 , the second contact plug 420 includes two types, one is the second contact plug 420a electrically connected to the gate metal 210 of the gate stack, and the other is the second contact plug 420b electrically connected to the first contact plug 320, by Figure 16 It can be seen that the second contact plug 420a is not on the same straight line as the two adjacent second contact plugs 420b. refer to Figure 17 to Figure 20 One or more second contact plugs 420a electrically connected to the gate metal 210 on the semiconductor structure and the two adjacent second contact plugs 420b electrically connected to the source / drain region 110 are not on the same straight line, which is also an embodiment The difference between the second embodiment and the first embodiment is that the advantage of this arrangement is that the second contact plug 420a and the second ...

Embodiment 3

[0072] On the basis of referring to the description of the same part in embodiment one or embodiment two, please refer to Figure 21 to Figure 23 . In certain cases, it is necessary to electrically connect the gate of a semiconductor structure to its source and drain, or to electrically connect the gate or source and drain of one semiconductor structure to the gate or source and drain of another nearby semiconductor structure. Such metal interconnections can be realized locally in the cap layer 400 . For example, according to the design requirements, the electrical connection between the gate and its source and drain is made, such as Figure 22 As shown, the size and shape of the second contact plug 420 in the capping layer 400 can be adjusted so that it is electrically connected to the first contact plug 320 connected to the source / drain region 110 and the gate metal 210 at the same time. The advantage of setting the second contact plug 420 in this way is to realize the ele...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More