Delay time measurement circuit and delay time measurement method

A technology for delay time and measuring circuits, which is applied in the direction of electronic circuit testing, frequency measuring devices, and frequency-to-amplitude conversion. It can solve the problems of large occupied area and complicated circuit, and achieve simple structure, high accuracy, and small occupied area. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0035] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways than those described here, so the present invention is not limited by the specific embodiments disclosed below.

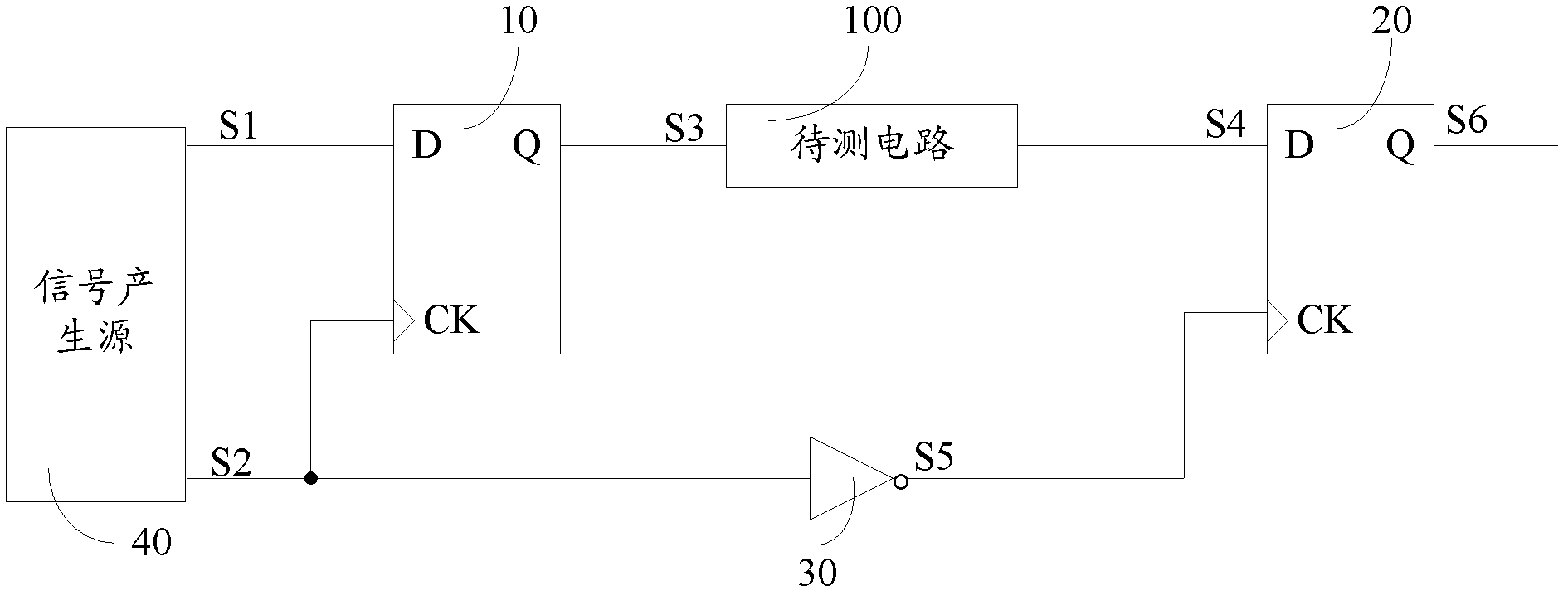

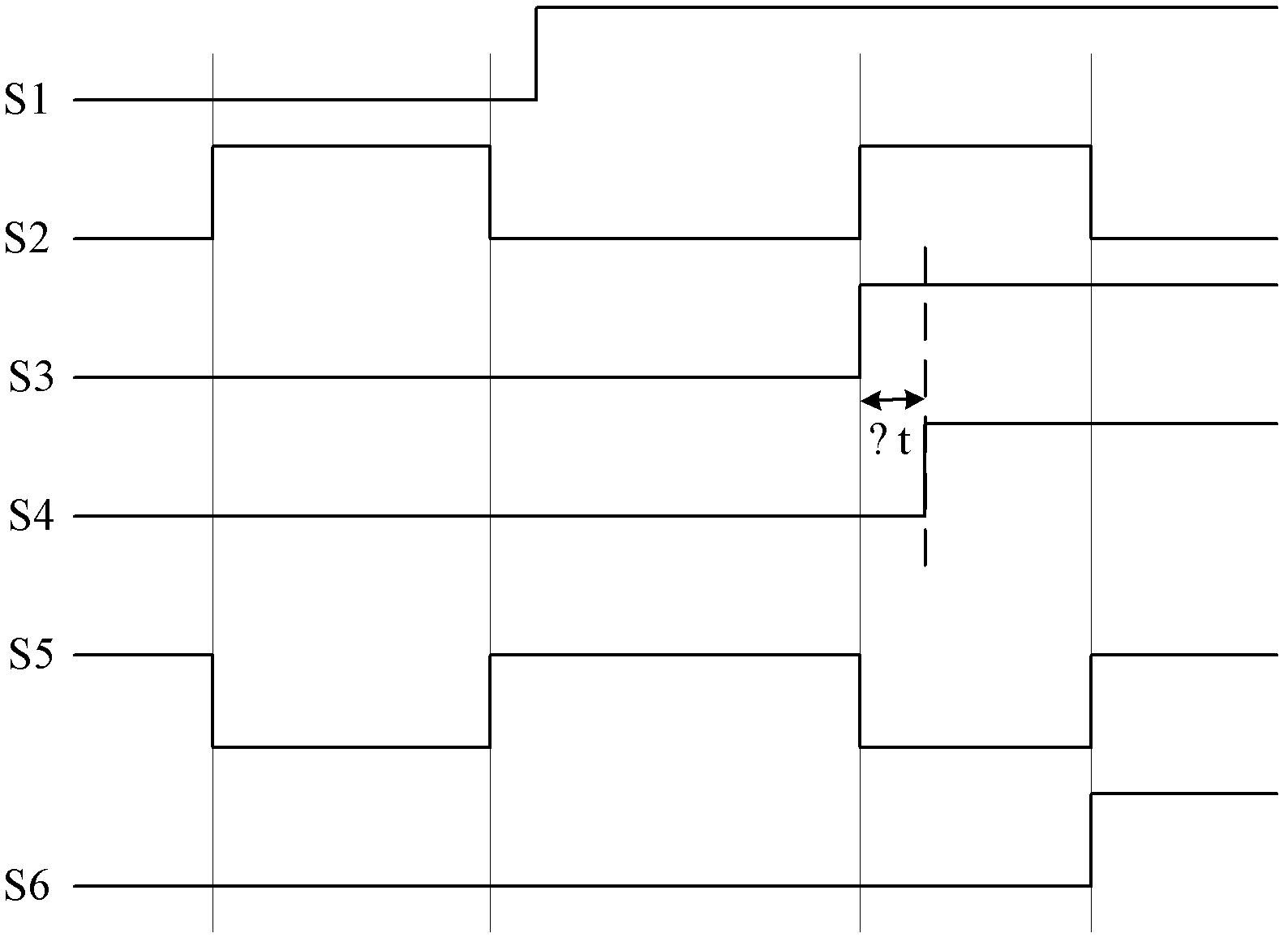

[0036]As mentioned in the background section, the circuit for measuring delay time in the prior art is relatively complicated and occupies a large area. In addition, refer to figure 1 As shown, the two D flip-flops and one inverter will cause a certain delay time to the passed signal, thus reducing the accuracy of delay time measurement.

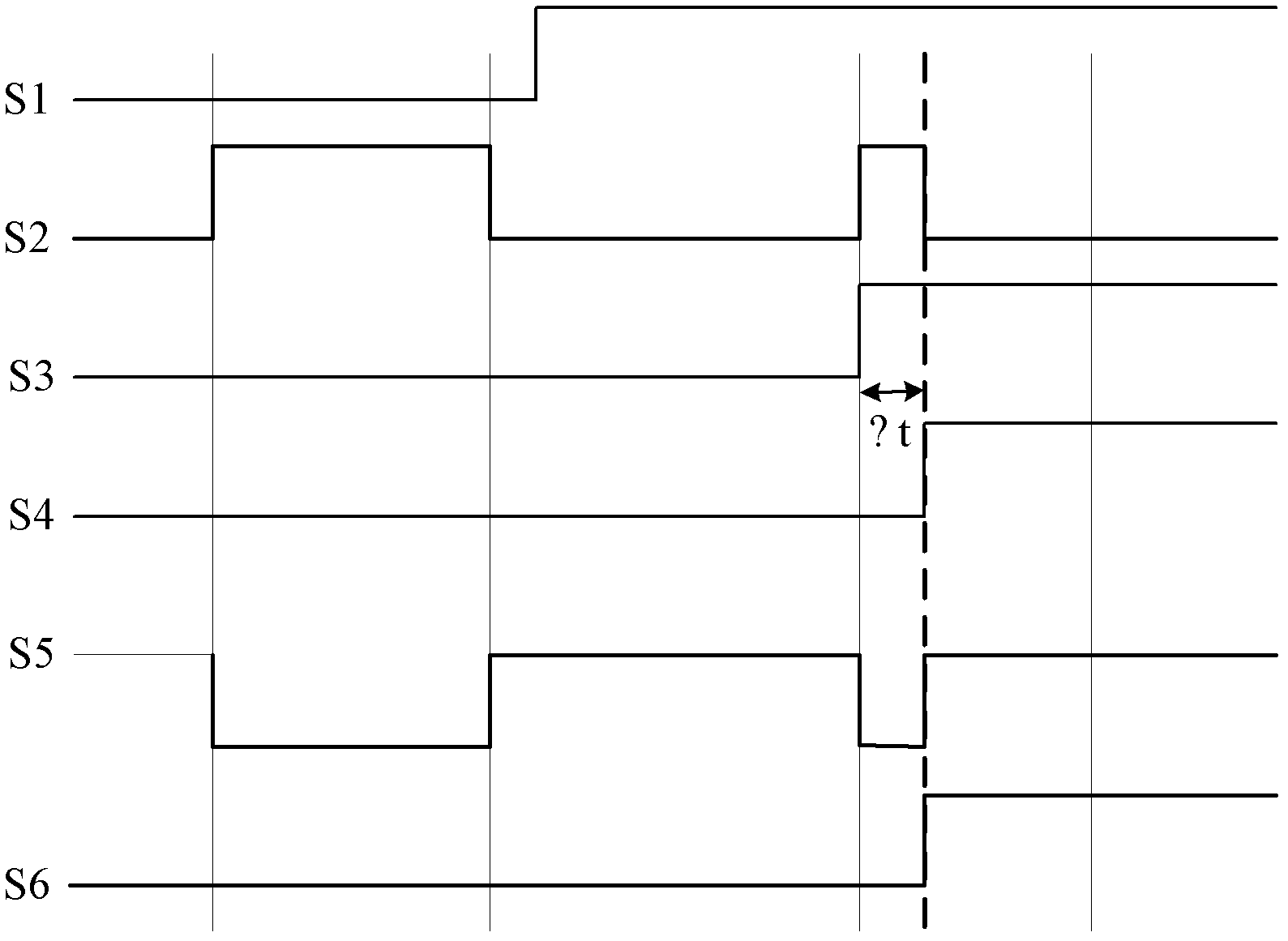

[0037] In view of the above-mentioned defects, the present invention provides a delay time measurin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More