Method for solving communication deadlock of I2C (Inter-Integrated Circuit) bus

A bus communication and solution technology, which is applied in the field of system bus communication, can solve problems such as signal processing complexity, increase system cost, increase cost, etc., achieve fast and accurate I2C bus communication deadlock problem, and solve I2C bus communication deadlock problem Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0047] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings, but they are not intended to further limit the present invention.

[0048] I 2 The C bus consists of a serial SDA data line and a serial SCL clock line; the I 2 The C bus is provided with a master and at least one slave. The slave is a module with programmable functions, such as a single-chip microcomputer or FPGA; the slave can also be a simple I 2 C-function interface devices, such as temperature sensors.

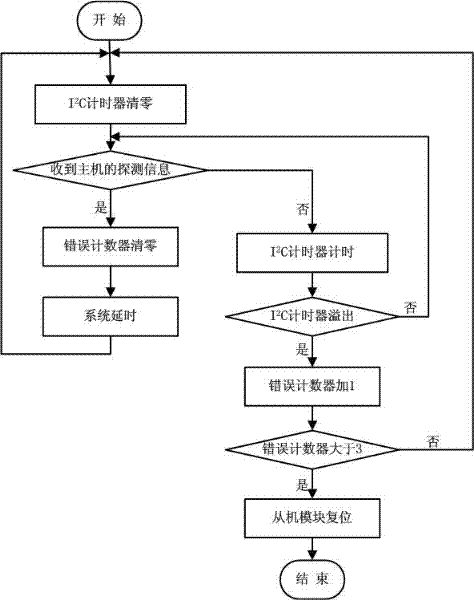

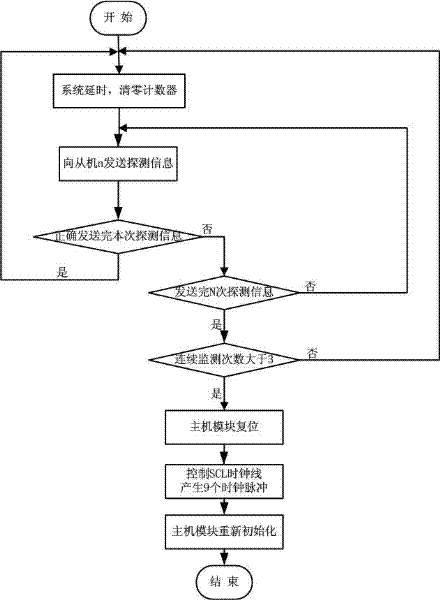

[0049] I 2 The C bus communication deadlock solution includes a host-based execution method and a programmable slave-based execution method.

[0050] The host-based execution method includes the following steps:

[0051] A. Monitoring I 2 The working status of the C bus; if the host cannot 2 C bus slave sends detection information, then I 2 The C bus is in a deadlock state;

[0052] B. When I 2 The C bus is in a deadlock state, th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More