Semiconductor device

A semiconductor and circuit layer technology, applied in the field of semiconductor devices with a thermoelectric cooling mechanism, can solve the problems of insufficient heat dissipation efficiency of high-density packaging components, and achieve the effect of easy heat dissipation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

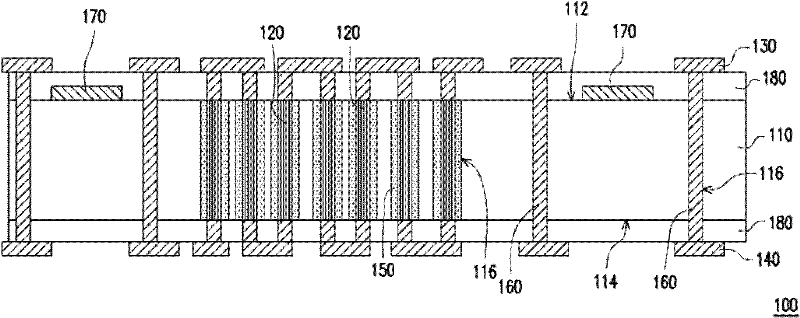

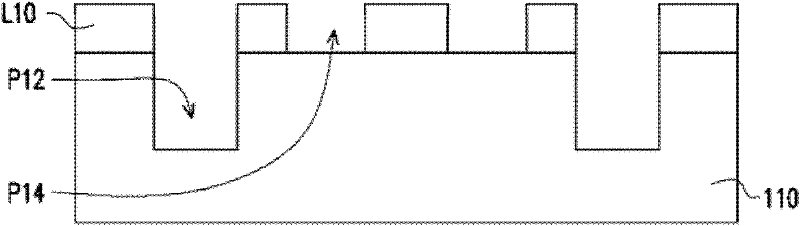

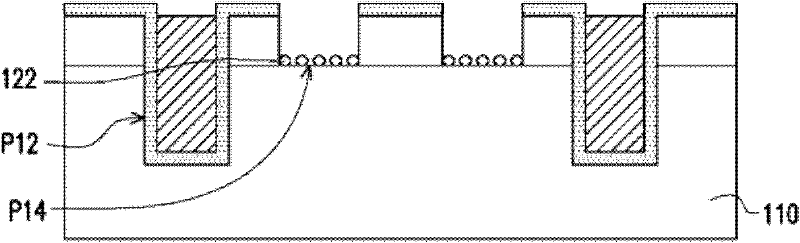

[0042] figure 1 is a cross-sectional view of a semiconductor device according to an embodiment of the present invention. Please refer to figure 1 The semiconductor device 100 of this embodiment includes a silicon substrate 110 , a plurality of silicon nanowire bundles 120 , a first circuit layer 130 and a second circuit layer 140 . The silicon substrate 110 has a first surface 112 and a second surface 114 opposite to each other and a plurality of through holes 116 . Each silicon nanowire bundle 120 is disposed in a through hole 116 . The first circuit layer 130 is disposed on the first surface 112 and electrically connected to the silicon nanowire bundle 120 . The second circuit layer 140 is disposed on the second surface 114 and electrically connected to the silicon nanowire bundle 120 .

[0043] In this embodiment, the silicon nanowire bundle 120 is, for example, directly fabricated from the silicon substrate 110 . Each silicon nanowire bundle 120 is, for example, a P-t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More