Through hole processing method and through hole processing system for on-chip power supply network simulation

A technology of power supply network and processing method, which is applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of complex power supply network structure, affecting the convergence and stability of power supply network simulator, and difficulty in simulation methods, etc. To achieve the effect of improving convergence and stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

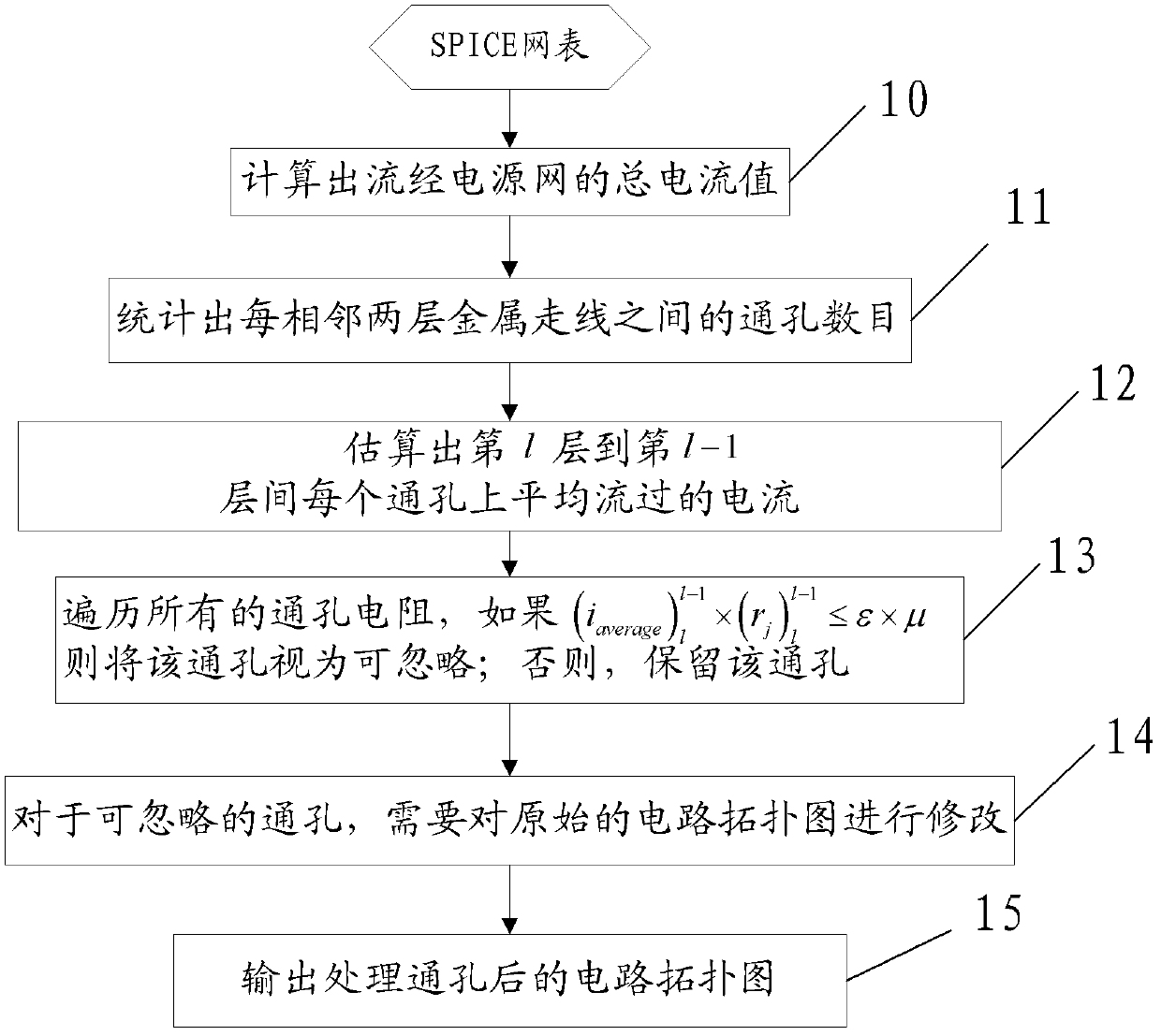

[0032] The invention proposes a method for adaptively processing through holes, under the condition of ensuring the solution accuracy, adaptively processes the number and position of through holes, updates the topological structure of the original circuit, thereby improving the convergence and stability of the problem to be solved . Specifically include the following:

[0033] 1. Matrix equation for power supply network simulation

[0034] According to the nodal analysis method to establish the system matrix equation, g ij Defines the conductance value between node i and node j, that is, g ij =g ji , so the coefficient matrix A has symmetry, and its diagonal elements where N i ={j|g ij ≠0} represents the set of nodes connected to node i, so matrix A is a sparse, symmetric, positive definite matrix.

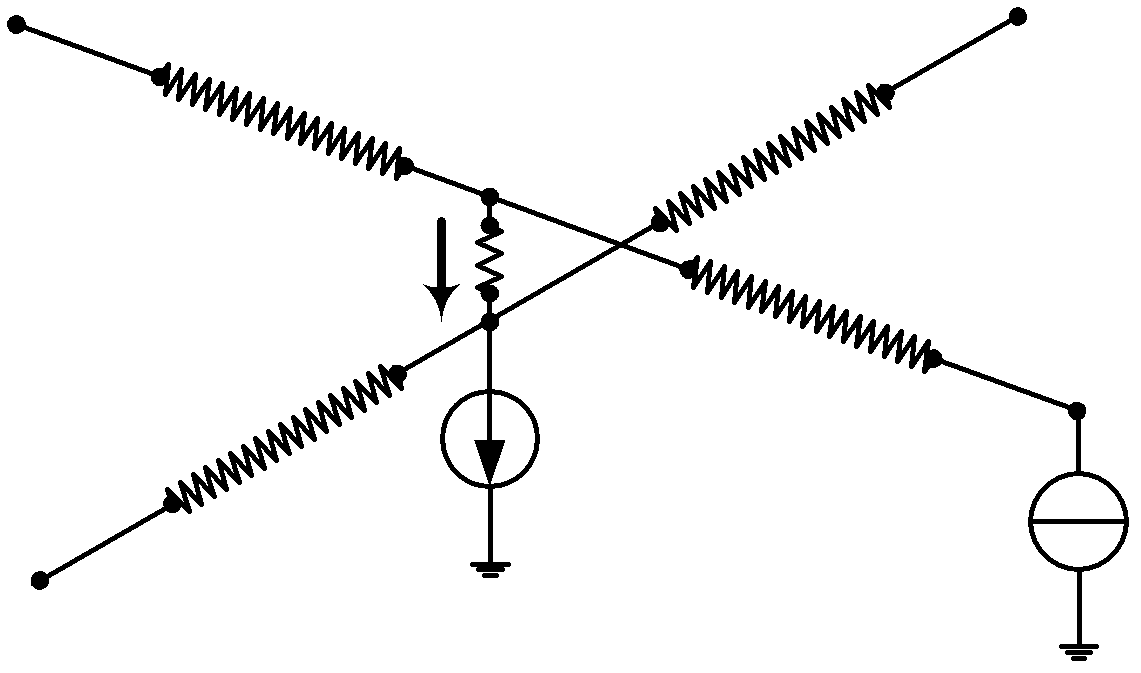

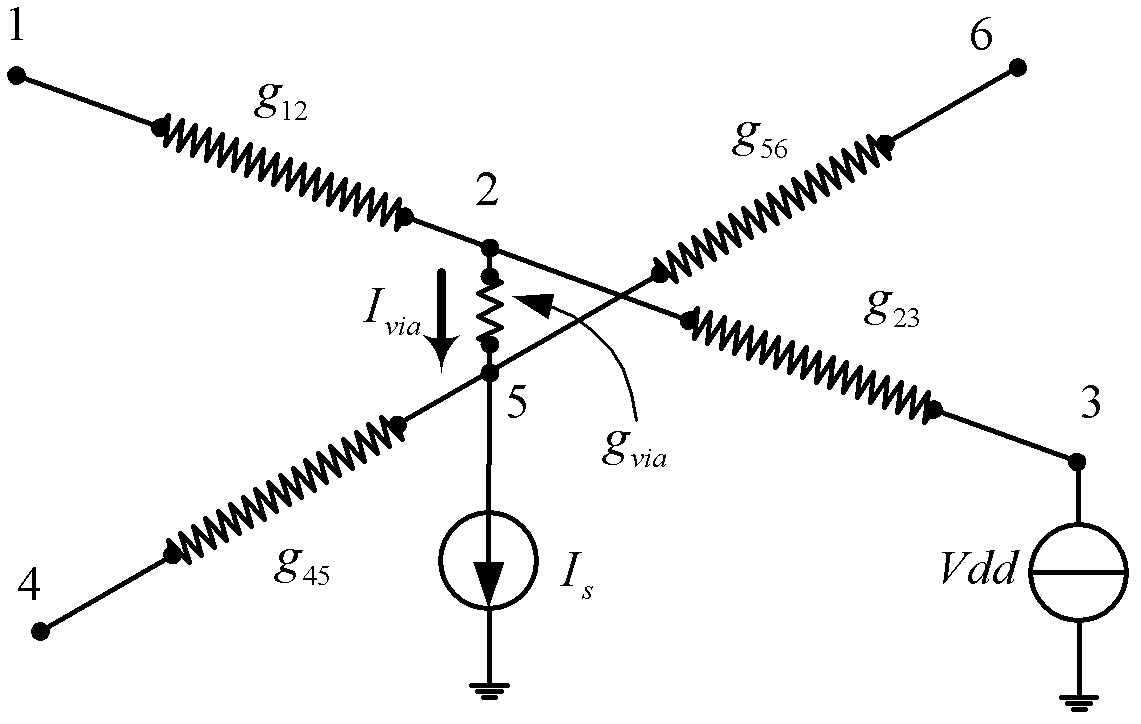

[0035] like figure 2 As shown, the conductance of the upper metal trace is g 12 with g 23 , the conductance of the lower metal trace is g 45 with g 56 , the via cond...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More