Method for forming bottom oxide layer in double-layered gate groove MOS (Metal Oxide Semiconductor) structure

A technology of MOS structure and bottom oxide layer, which is applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problem of increasing the capacitance between drain and source, and achieve the effect of reducing the capacitance between source and drain and reducing power loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

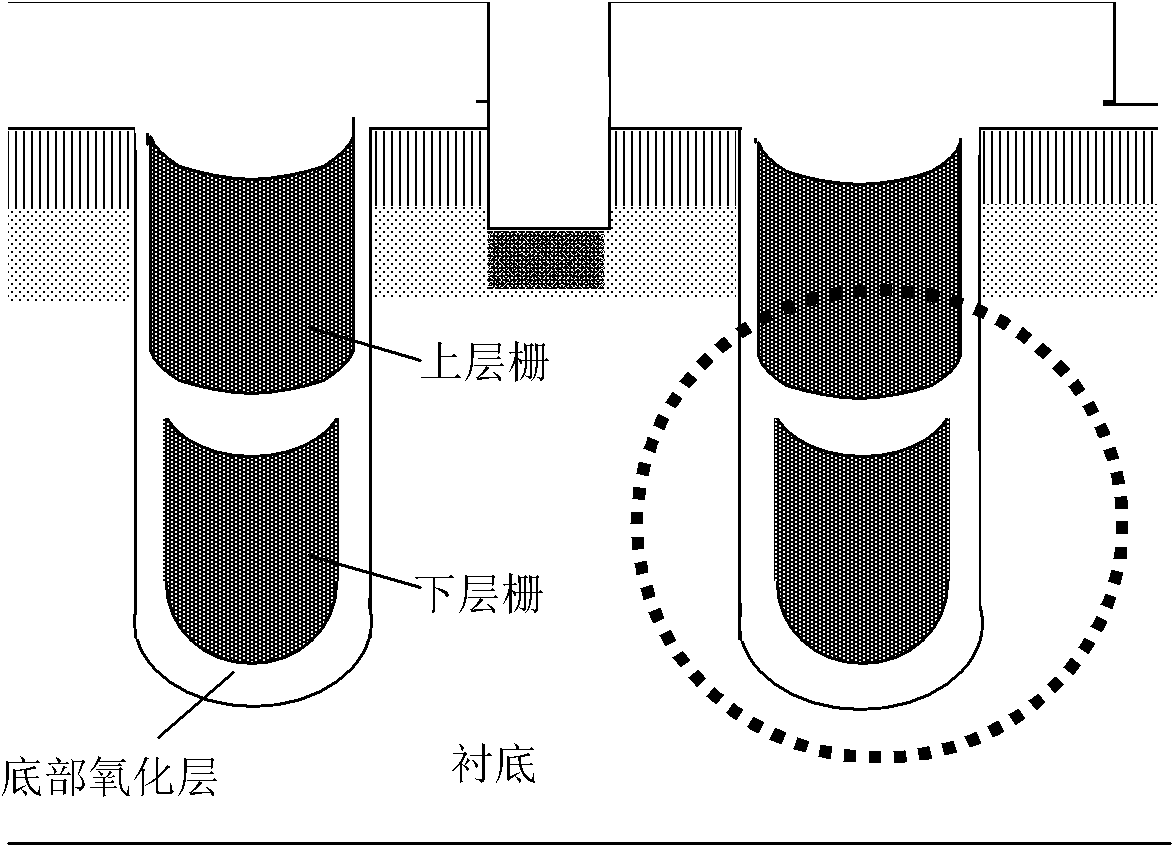

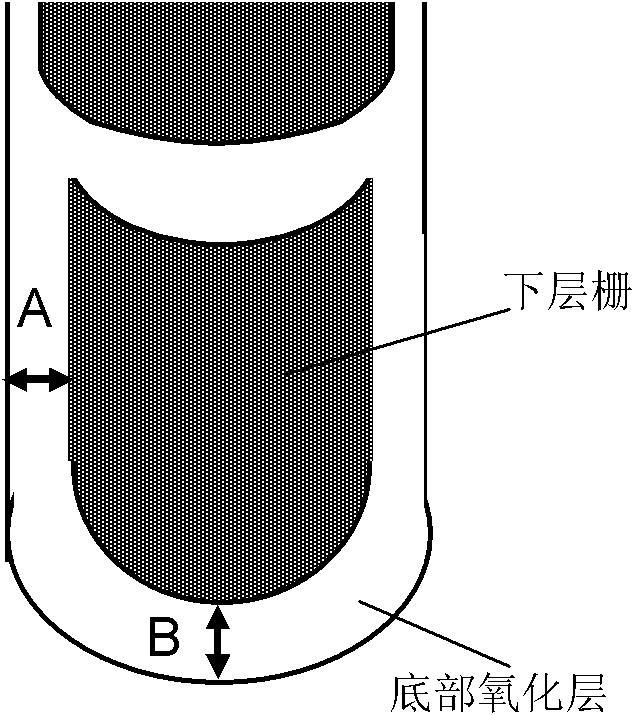

[0020] The method of the present invention is to reduce the source-drain capacitance through the thick bottom oxide layer on the existing double-layer gate trench MOS, and then effectively reduce its high-frequency operation on the basis of the original advantages of the double-layer gate trench MOS. under the power loss.

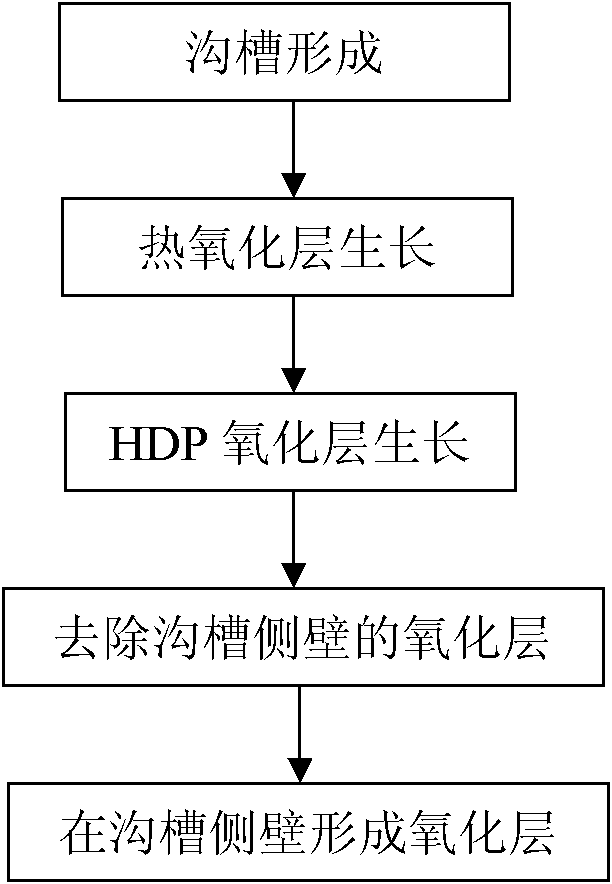

[0021] The method for forming the bottom oxide layer in the double-layer gate trench MOS structure of the present invention, see image 3 The process is described in detail below.

[0022] After trench formation (see Figure 5 ), first grow an oxide layer on the inner wall of the trench and the surface of the substrate, usually by thermal oxygen oxidation (see Image 6 ). The trench is etched using a conventional dry etching process. The depth and width of the trench are the same or similar to those of the existing double-layer gate trench MOS device. The thermal oxide layer is grown by using a thermal oxygen process to oxidize silicon to form an oxide...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More