Method and system for large-scale integrated circuit channel wiring based on parallel computation

A large-scale integrated circuit, parallel computing technology, applied in computing, electrical digital data processing, special data processing applications, etc., to achieve the effect of solving the problem of interconnect crosstalk

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

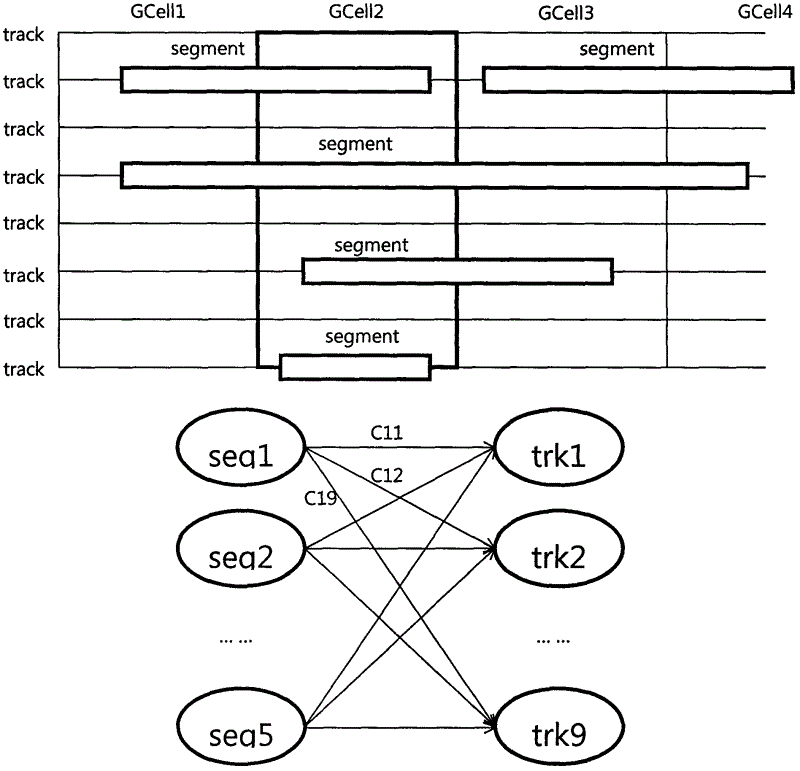

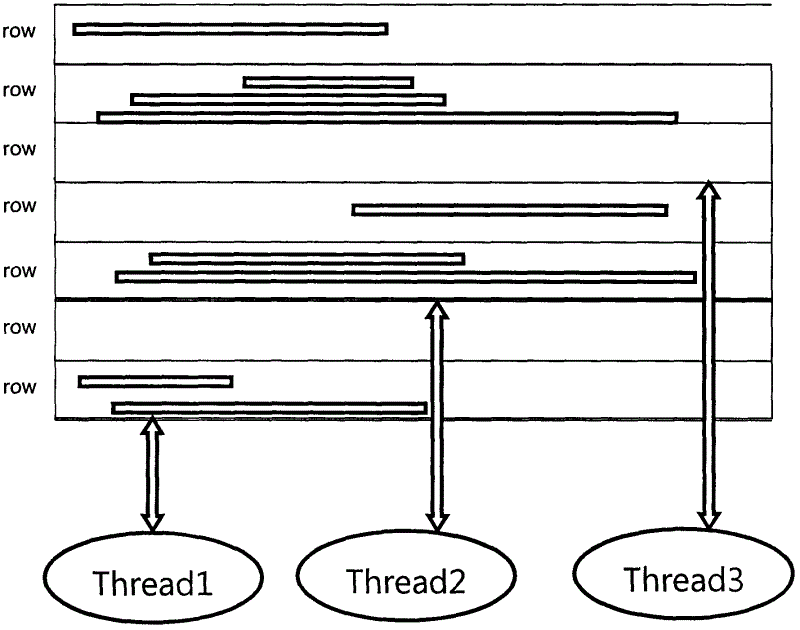

[0033] This embodiment designs a channel routing method for large-scale integrated circuits based on parallel computing. The channel routing problem on different layers is divided into channel routing sub-problems in each routing unit row, and then these sub-problems are abstracted into a series of The linear allocation problem inside the routing unit. The object to be allocated in this problem is the wiring segment of different nets inside the wiring unit, and the allocated containers are different routing channels, such as figure 1 shown. This method is based on a distributed computing framework. For the channel routing sub-problem to be processed, it is processed in parallel by multi-threading, such as figure 2 shown. For the linear allocation problem inside each routing unit, this method optimizes these objectives by minimizing the al...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More