Chip scale package (CSP) chip mounting loading device and mounting method

A chip mounting and carrier technology, which is applied to the assembly of printed circuits with electrical components, electrical components, semiconductor/solid-state device manufacturing, etc., can solve the problems of accumulative errors that cannot be produced in multiple chips, high equipment costs, etc., and improve the welding yield. and straight-through rate, optimize the mass production process, and reduce the effect of equipment investment cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

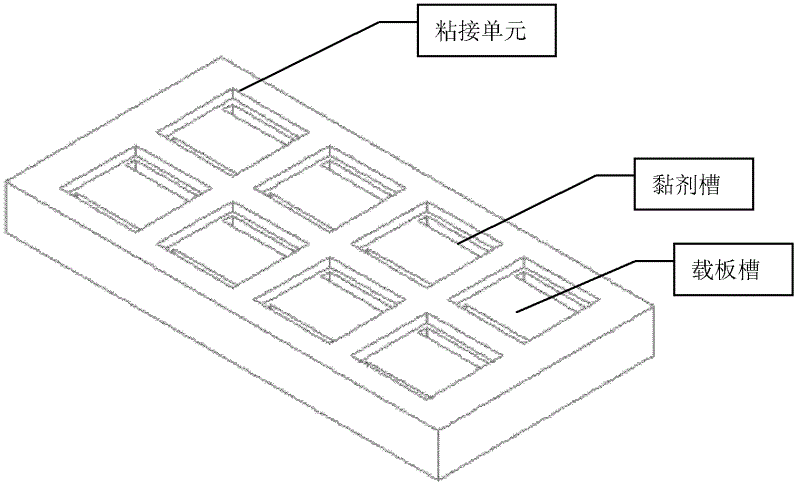

[0021] Such as figure 1 As shown, the CSP die-attaching carrier described in the present invention is provided with a plurality of bonding units on the carrier, and the bonding unit includes a carrier groove for placing a carrier to be mounted, and a Adhesive groove on the edge of the carrier board groove to be mounted, where the adhesive used to stick the carrier board to be mounted is placed.

[0022] The carrier and the bonding unit are rectangular.

[0023] The bonding units are arranged symmetrically with respect to the perpendicular to the opposite sides of the rectangle formed by the carrier.

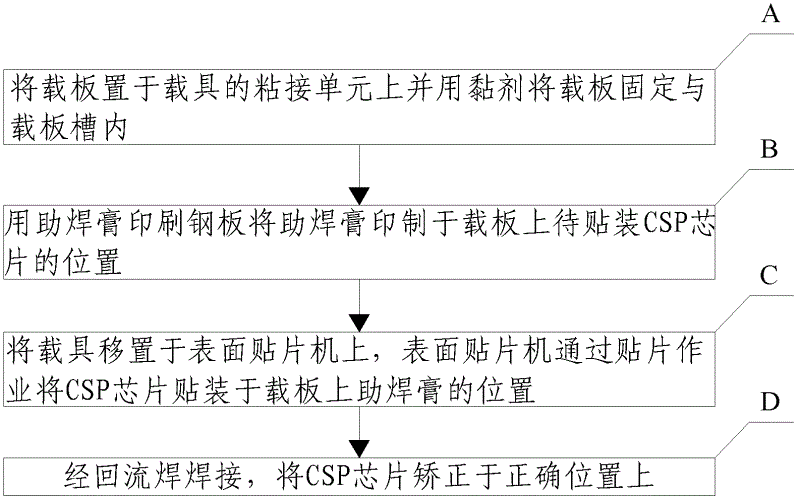

[0024] Such as figure 2 As shown, the method for mounting the CSP c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More