Novel static random access memory (SRAM) storage unit preventing single particle from turning

An anti-single-event and memory cell technology, applied in the field of new anti-single-event inversion SRAM memory cells, can solve the problems of long inversion recovery time affecting the operating frequency, transistors cannot be completely turned off, and short inversion recovery time, etc. Simple and reliable, reducing the rollover recovery time, and the effect of reducing rollover recovery time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The invention will be described in further detail below in conjunction with the accompanying drawings.

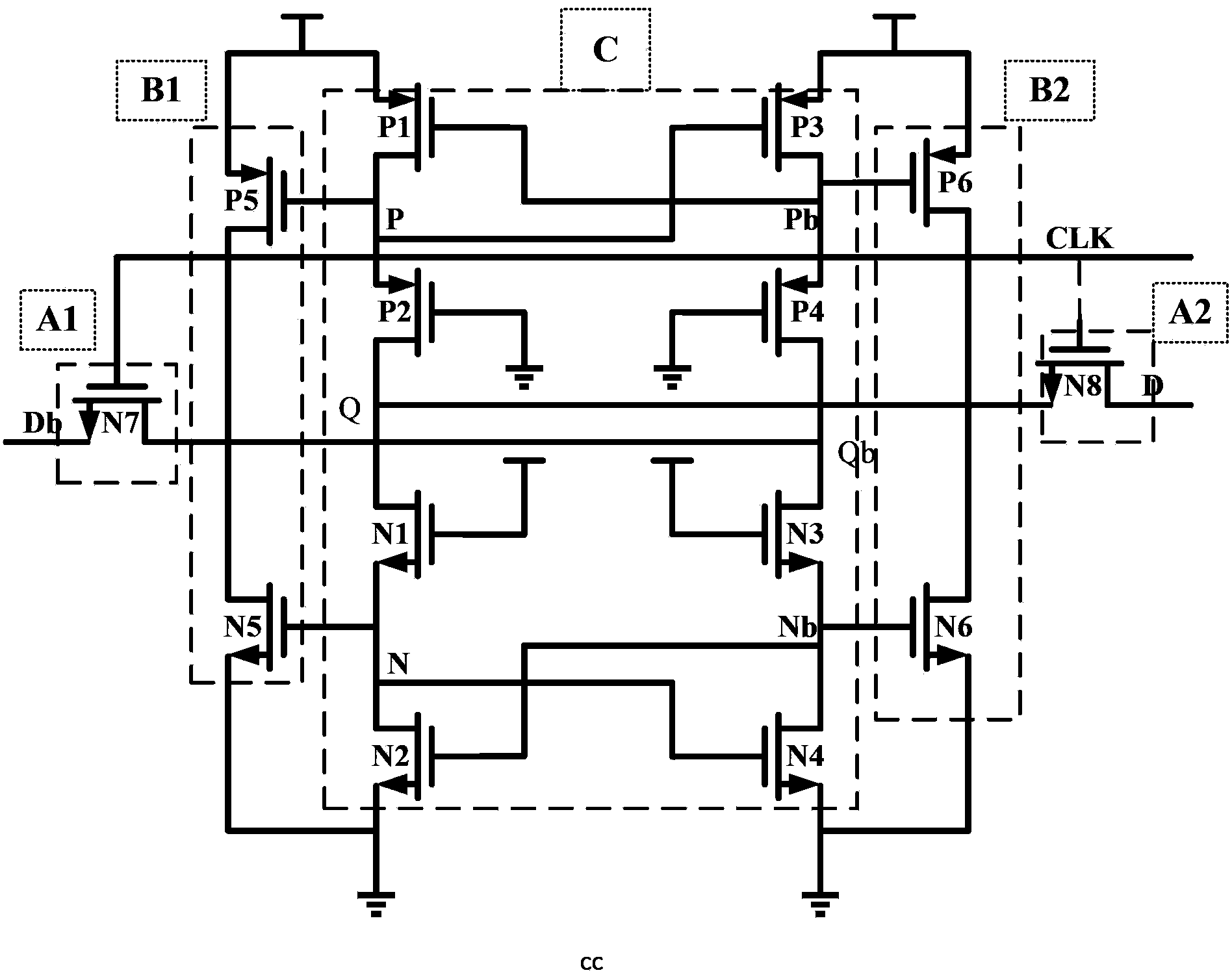

[0018] The circuit structure of the SRAM storage unit of the present invention is as figure 1 As shown (where CLK is the clock signal, and D and DB are data input and output signals), it includes the first input and output port A1, the first potential reversal recovery drive circuit B1, the voltage holding circuit C, and the second potential reversal recovery drive connected in series. The circuit B2 and the second input and output port A2 include: 8 NMOS transistors and 6 PMOS transistors. Among them, P, Pb, Q, Qb, N, and Nb are internal nodes of the SRAM storage unit. The connection method is: the gate of PMOS transistor P1 is connected to node Pb, the drain is connected to node P, the source and substrate are connected to power supply VDD; the gate of POMS transistor P2 is grounded, the drain is connected to node Q, the source is connected to node P, and the subs...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More