On-chip network node communication method based on macro virtual channel

A communication method and network-on-chip technology, applied in the direction of data exchange network, digital transmission system, electrical components, etc., can solve problems such as limited address space, susceptibility to electromagnetic interference, scalability problems, etc., and achieve the effect of solving information transmission errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

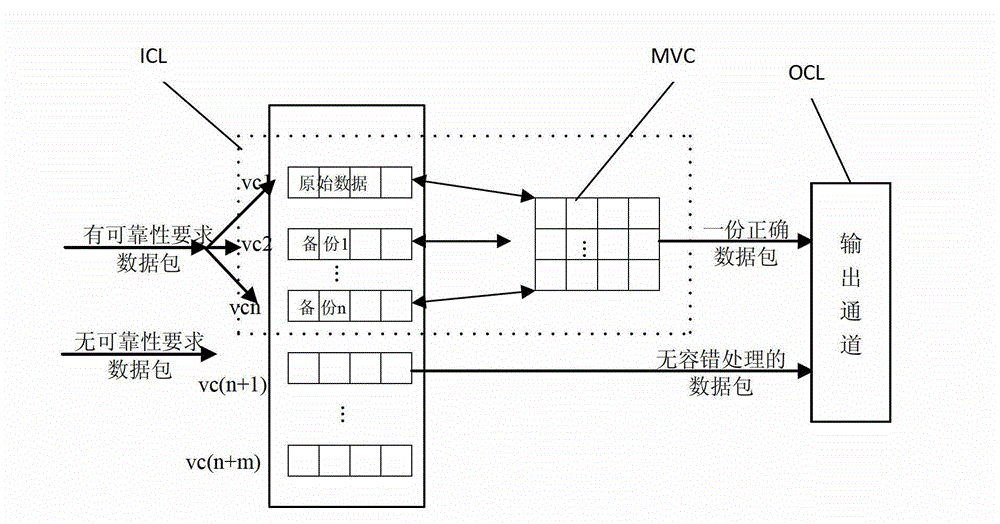

[0007] Specific implementation mode one: the following combination figure 2 This embodiment will be specifically described. This embodiment is realized through the following process: one, from another data packet of communication node, enters this communication node router; data packet; two copies of backup data packets are copied for reliability requirements data packets; two, two copies of backup data packets of reliability requirements data packet and its duplication enter three virtual channels of input register ICL respectively; meanwhile, reliable The reliability requirement data packet and the two backup data packets it replicates send an application signal to the virtual channel allocator VCA. If the application is approved, the reliability requirements data packet and the two backup data packets it replicates enter the macro virtual channel MVC respectively. , in the macro-virtual channel MVC, according to the principle that the minority is subject to the majority, ...

specific Embodiment approach 2

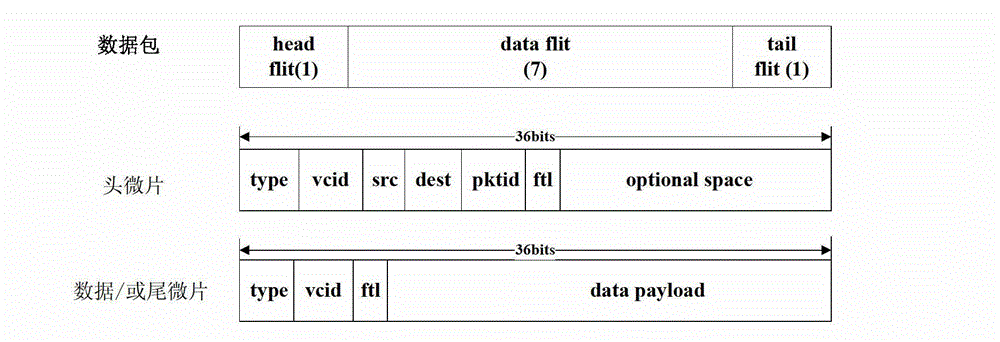

[0009] Specific implementation mode two: the following combination figure 1 with figure 2 This embodiment will be specifically described. The difference between this embodiment and Embodiment 1 is: in step 2, when the data packet has reliability requirements, the virtual channel allocator VCA checks the status of the three virtual channels of the macro virtual channel, if they are idle, release For the locking of the macro-virtual channel, complete the three-mode redundancy judgment of the reliability-required data packet and the two backup data packets copied in the macro-virtual channel MVC; if the status of the three virtual channels is not idle, return None Channel allocation command, lock the three virtual channels of the macro-virtual channel, and wait for the three virtual channels to be idle at the same time before allocating the macro-virtual channel;

[0010] When the data packet has no reliability requirement, the virtual channel allocator VCA checks whether the ...

specific Embodiment approach 3

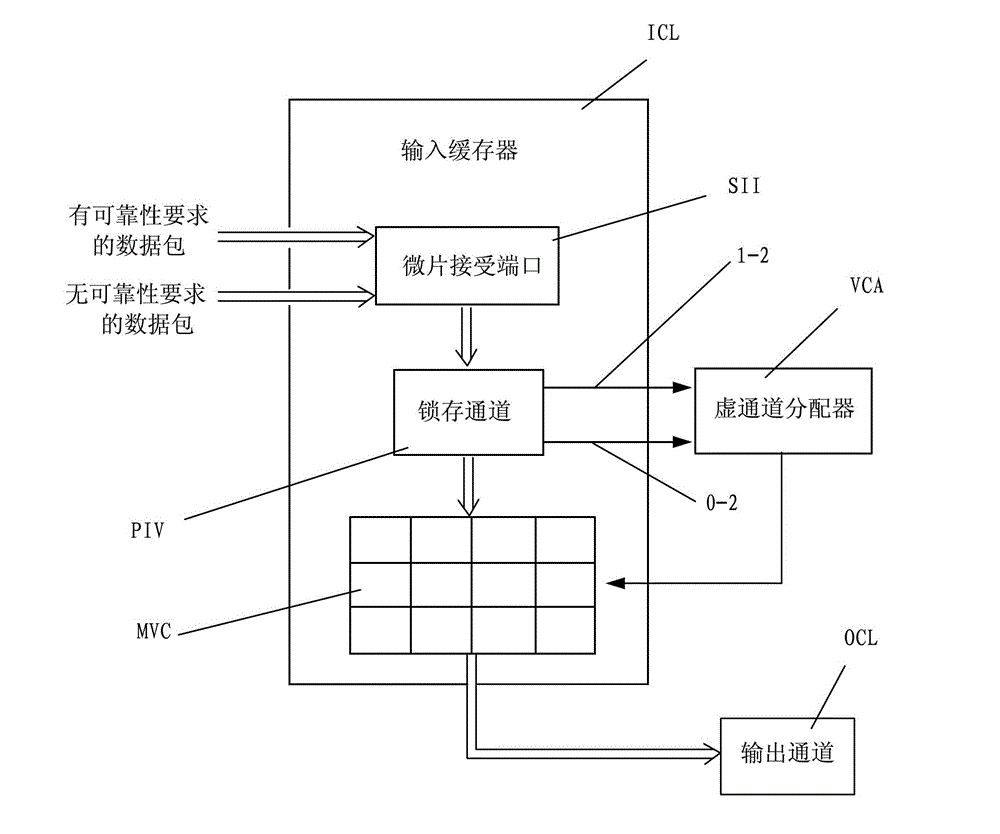

[0015] Specific implementation mode three: the following combination image 3 This embodiment will be specifically described. The difference between this embodiment and embodiment two is that in step two, the data packet with reliability requirements arrives at the microchip accepting port SII of the input channel, then enters the latch channel PIV, and passes through the signal line 1-2 to the virtual channel The controller VCA applies for a virtual channel, and the virtual channel allocator VCA checks the status of the three virtual channels of the macro virtual channel VCA; if they are idle, the latch channel PIV unlocks the macro virtual channel VCA, and sends data packets with reliability requirements Transmission and three-mode redundancy judgment; if the macro-virtual channel VCA is not idle, return no virtual channel to allocate, and the latch channel PIV locks the three virtual channels of the macro-virtual channel, and waits for the three virtual channels to be idle ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More