High-accuracy fine adjustment method for charge coupled device (CCD) video signal sampling timing sequence

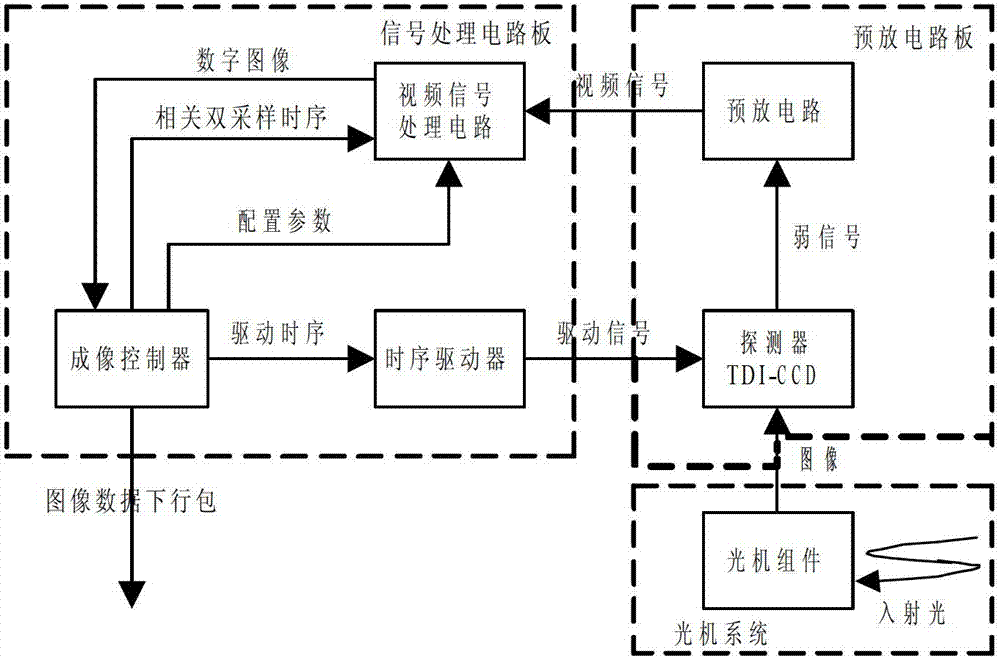

A technology of video signal and sampling timing, which is applied in the field of fine-tuning the sampling timing of high-precision CCD video signals, can solve the problems that the adjustment accuracy cannot meet the requirements and the flexibility of timing adjustment is poor, and achieves the effect of improving image quality and adjustment accuracy.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

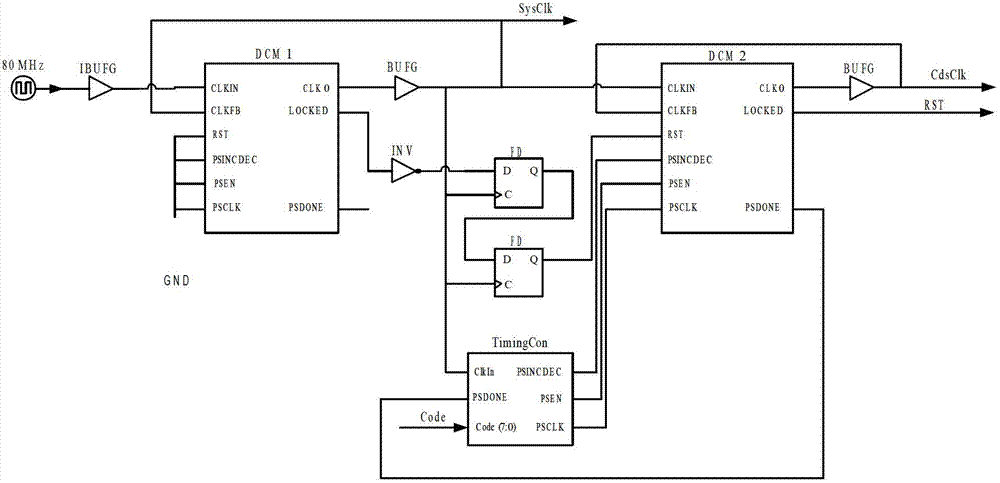

[0023] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments.

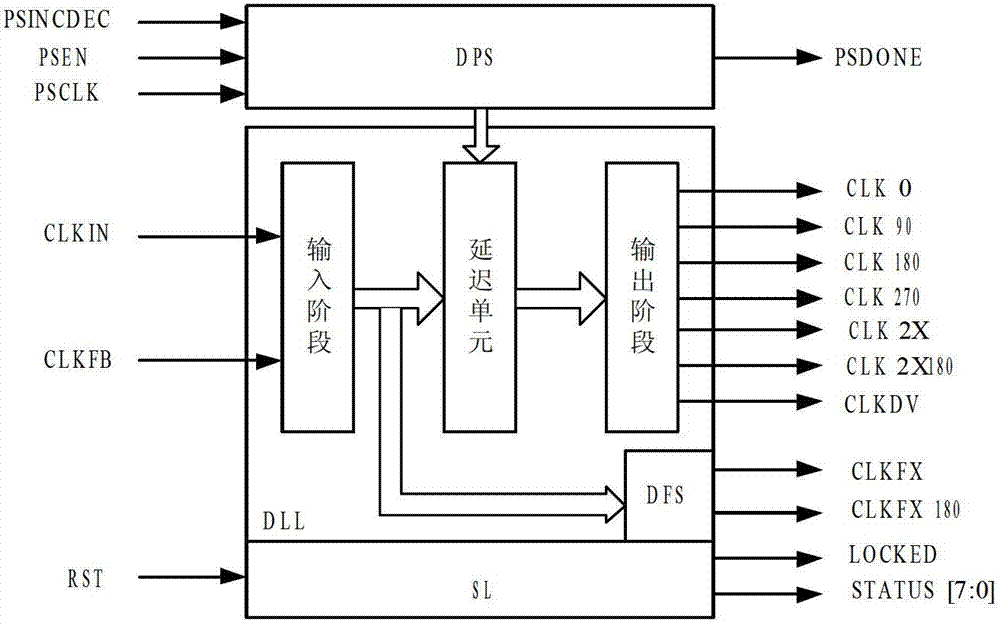

[0024] DCM (digital clock manager) is a firmware resource integrated in Xilinx FPGA for clock synthesis, clock skew elimination and clock phase adjustment. It consists of four independent functional units, namely DLL (Delay- Locked Loop delay locked loop), DFS (Digital Frequency Synthesizer digital frequency synthesizer), DPS (Digital Phase Shift digital phase shifter) and SL (Status Logic state logic), its internal structure is as follows figure 2 shown.

[0025] DLL is the core component of DCM, its input pins are CLKIN and CLKFB, and its output pins are CLK0, CLK90, CLK180, CLK270, CLK2X, CLK2X180 and CLKDV. It is typically used in system synchronization design (the two FPGAs for data transmission use the same external crystal oscillator), the data receiving FPGA needs to adjust the phase relationship between the clock and the data throug...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com