Method for post-processing blind hole of circuit board

A processing method and circuit board technology, applied in the direction of forming the electrical connection of printed components, etc., can solve the problems of insufficient electroplating and deep plating capacity, increase production cost, long processing time, etc., to save production time, production cost, and reduce processing difficulty. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0023] In order to fully understand the technical content of the present invention, the technical solutions of the present invention will be further introduced and illustrated below in conjunction with specific examples, but not limited thereto.

[0024] Such as Figure 2 to Figure 4 As shown, a post-processing method of a circuit board blind hole of the present invention, the method is a post-processing for the blind hole of a circuit board, comprising the following steps:

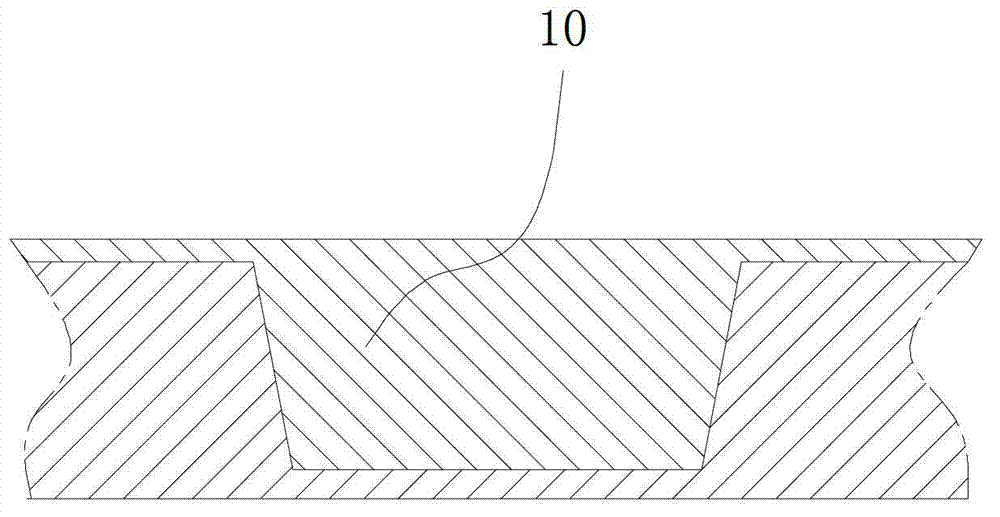

[0025] First, copper-plate the inner wall of the blind hole of the circuit board, and the thickness of the copper plating is 20-25um, such as figure 2 shown;

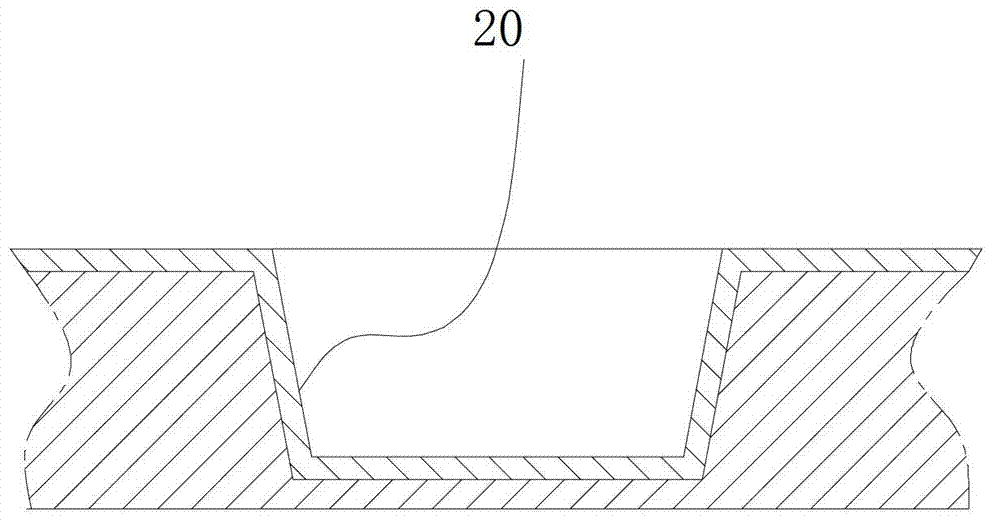

[0026] Secondly, vacuum plug the copper-plated blind hole, and grind the filling surface of the blind hole, such as image 3 shown;

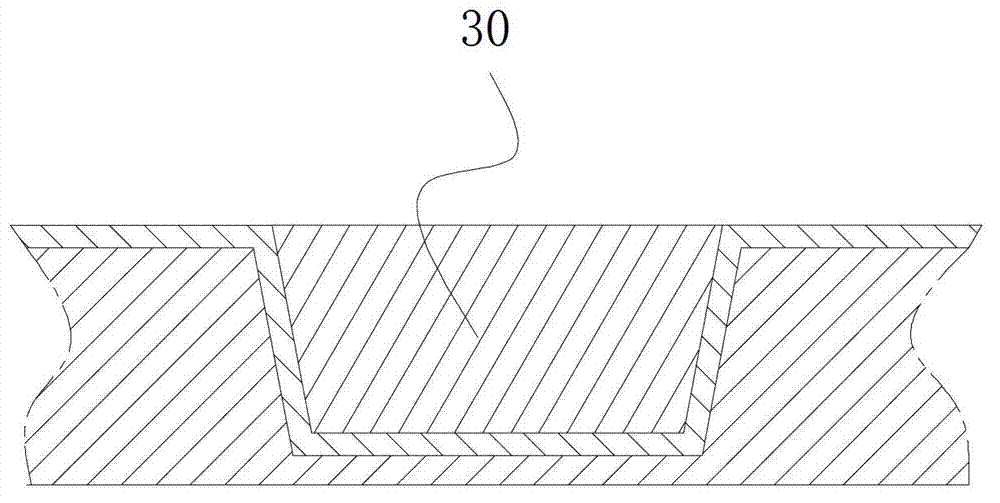

[0027] Finally, copper plating is carried out on the surface of the filled blind hole after grinding, and the thickness of the copper plating on the surface is 10-15um, such as Figure 4 shown;

[0028] Wherein...

PUM

| Property | Measurement | Unit |

|---|---|---|

| dielectric loss | aaaaa | aaaaa |

| dielectric loss | aaaaa | aaaaa |

| dielectric loss | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More