MPC8280 minimum system applying CPLD (complex programmable logic device) and state switching method for setting hard reset configuration words

A hard reset and minimal technology, applied in data reset devices, electrical digital data processing, instruments, etc., can solve the problems that the watchdog timing period cannot be increased, PowerPC cannot be shortened, etc., and achieve the effect of simple and reliable operation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

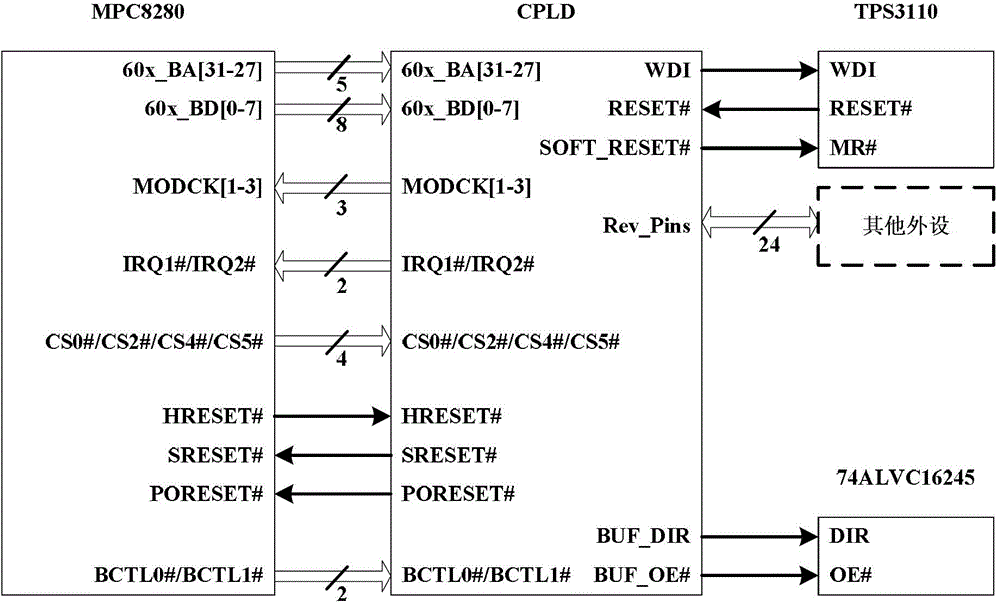

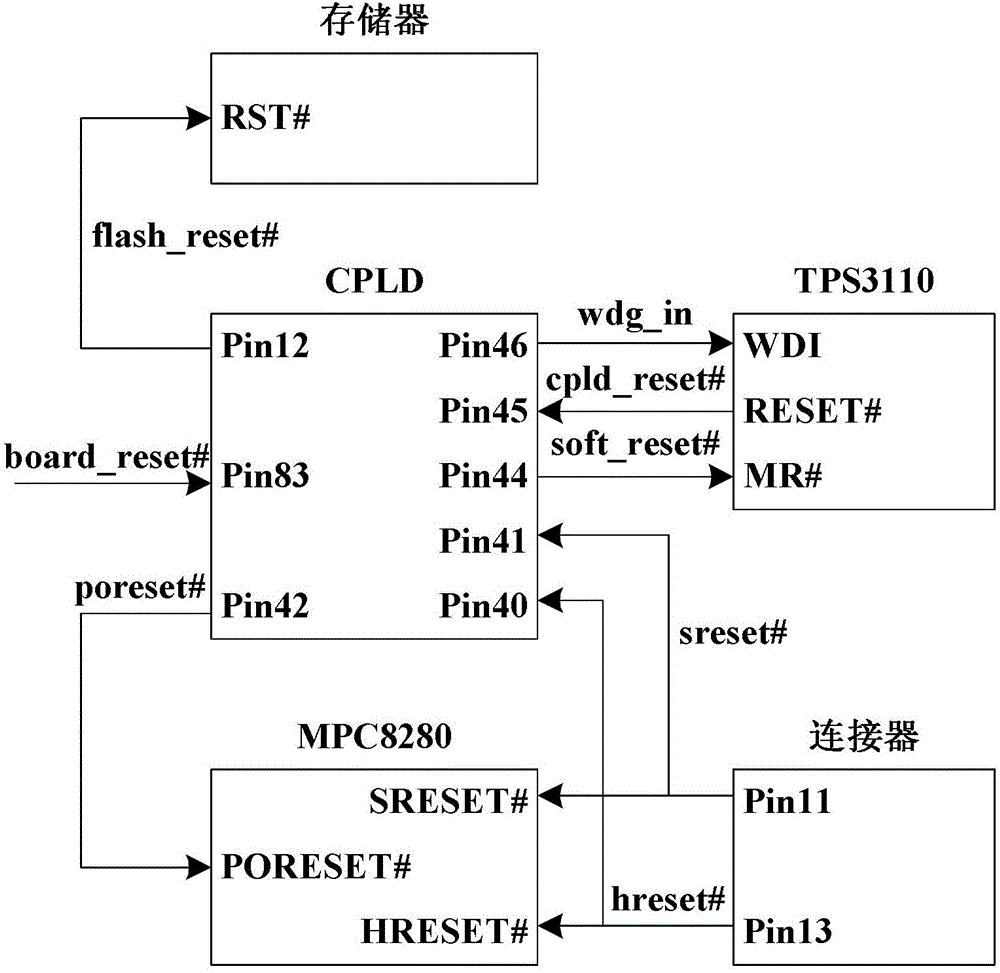

[0039] Specific implementation mode one: the following combination figure 1 Describe this embodiment, the MPC8280 minimum system of the application CPLD described in this embodiment, it comprises MPC8280, CPLD and TPS3110, the address bus signal output pin 60x_BA[31-27] of MPC8280 and the address bus signal input pin 60x_BA of CPLD [31-27] connect;

[0040] The data bus 60x_BD[0-7] of MPC8280 is connected to the data bus 60x_BD[0-7] of CPLD;

[0041] The level signal output pin MODCK[1-3] of CPLD is respectively connected with the clock hardware configuration pin MODCK[1-3] of MPC8280;

[0042] The interrupt signal output pin IRQ1# / IRQ2# of CPLD is respectively connected with the interrupt signal input pin IRQ1# / IRQ2# of MPC8280;

[0043] The chip selection signal output terminal of MPC8280 is connected with the chip selection signal input terminal of CPLD;

[0044] The output end of the hard reset signal pin HRESET# of the MPC8280 is connected to the input end of the hard ...

specific Embodiment approach 2

[0051] Specific implementation mode two: the following combination figure 1 Describe this embodiment. This embodiment is a further description of the clock hardware configuration pin MODCK[1-3] of the MPC8280 in Embodiment 1. The clock hardware configuration pin MODCK[1-3] of the MPC8280 described in this embodiment The state of is set by the following methods:

[0052] For applications that do not need to dynamically change the working clock of the MPC8280 core and CPM, use initialization to set the state of the output to the MODCK[1-3] pin during logic design;

[0053] For applications that do not need to dynamically change the MPC8280 core but need to change the CPM working clock, reset the initial value during logic design and program it into the CPLD;

[0054] For applications that need to dynamically change the working clock of the MPC8280 core and CPM but reprogram the CPLD, the 3 bits in the internal register of the custom CPLD correspond to MODCK[1-3]. By writing dat...

specific Embodiment approach 3

[0055] Specific implementation mode three: the following combination figure 1 Describe this embodiment mode, combine below figure 1 Describe this embodiment, this embodiment is the further explanation to the MPC8280 of embodiment one to the read and write operation of CPLD internal register, the implementation method of MPC8280 described in this embodiment to the read and write operation of CPLD internal register is:

[0056] Write register, when the CPLD chip select signal CS2# and write enable signal are valid, store the value on the data line in the register at the address specified by the address bus; read register, when the CPLD chip select signal and read enable signal are valid , read the value in the register of the address specified by the address bus into the data line.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com