Manufacturing method of memory

A manufacturing method and memory technology, applied in the field of memory, can solve problems such as difficulty in further improving memory element characteristics, affecting peripheral area element characteristics, gate characteristic degradation, etc., and achieve the effect of enhanced and good element characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

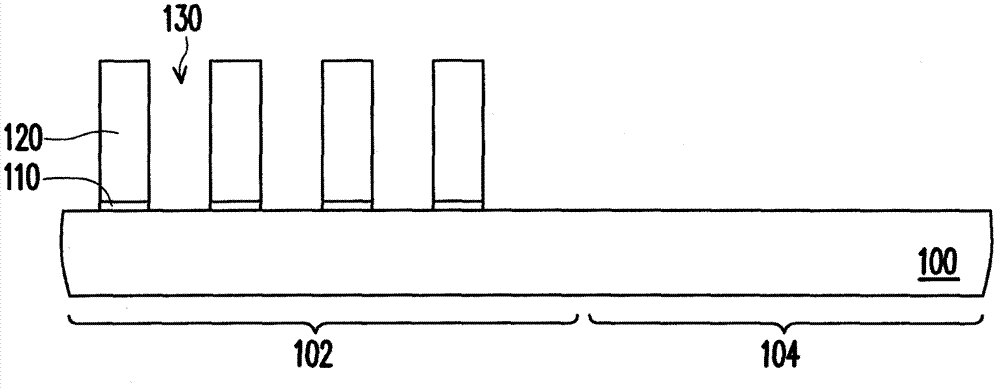

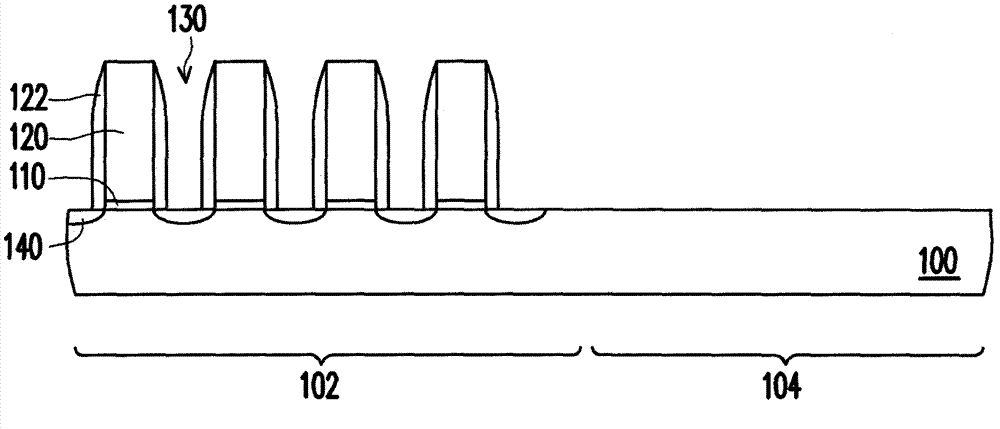

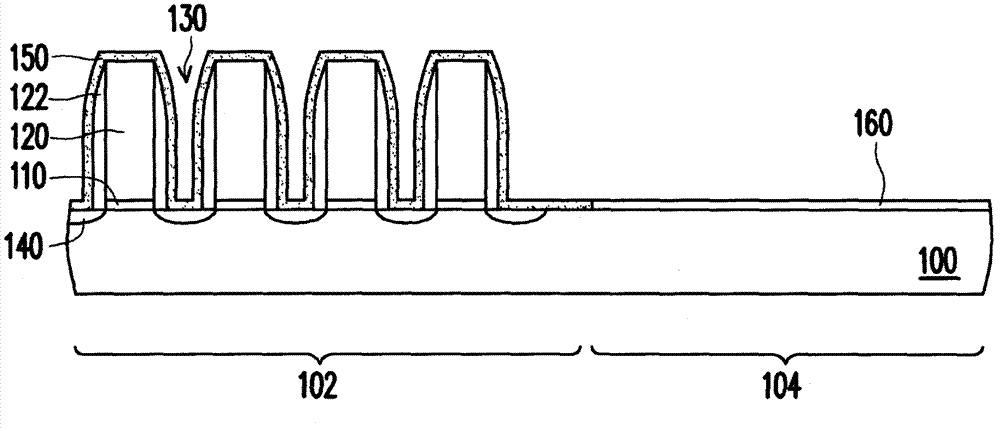

[0021] Figure 1A to Figure 1I It is a schematic cross-sectional view of a process of a method for manufacturing a memory according to an embodiment of the present invention.

[0022] Please refer to Figure 1A First, a substrate 100 is provided. The substrate 100 includes a memory cell region 102 and a peripheral region 104, wherein the memory cell region 102 is formed with a plurality of first gates 120 with a plurality of first openings 130 between the first gates 120. In this embodiment, it further includes forming a gate dielectric layer 110 between each first gate 120 and the substrate 100. The substrate 100 is, for example, a semiconductor substrate, such as an N-type or P-type silicon substrate, a group three or five semiconductor substrate, and the like. The gate dielectric layer 110 has, for example, a silicon oxide / silicon nitride / silicon oxide (ONO) structure. The material of the first gate 120 is, for example, doped polysilicon.

[0023] Please refer to Figure 1B The...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More