Sampling clock synchronizing method and system

A sampling clock synchronization, sampling pulse technology, applied in time division multiplexing systems, electrical components, multiplexing communications, etc., can solve the problems of error accumulation, hardware requirements and high cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the technical problems, technical solutions and beneficial effects to be solved by the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

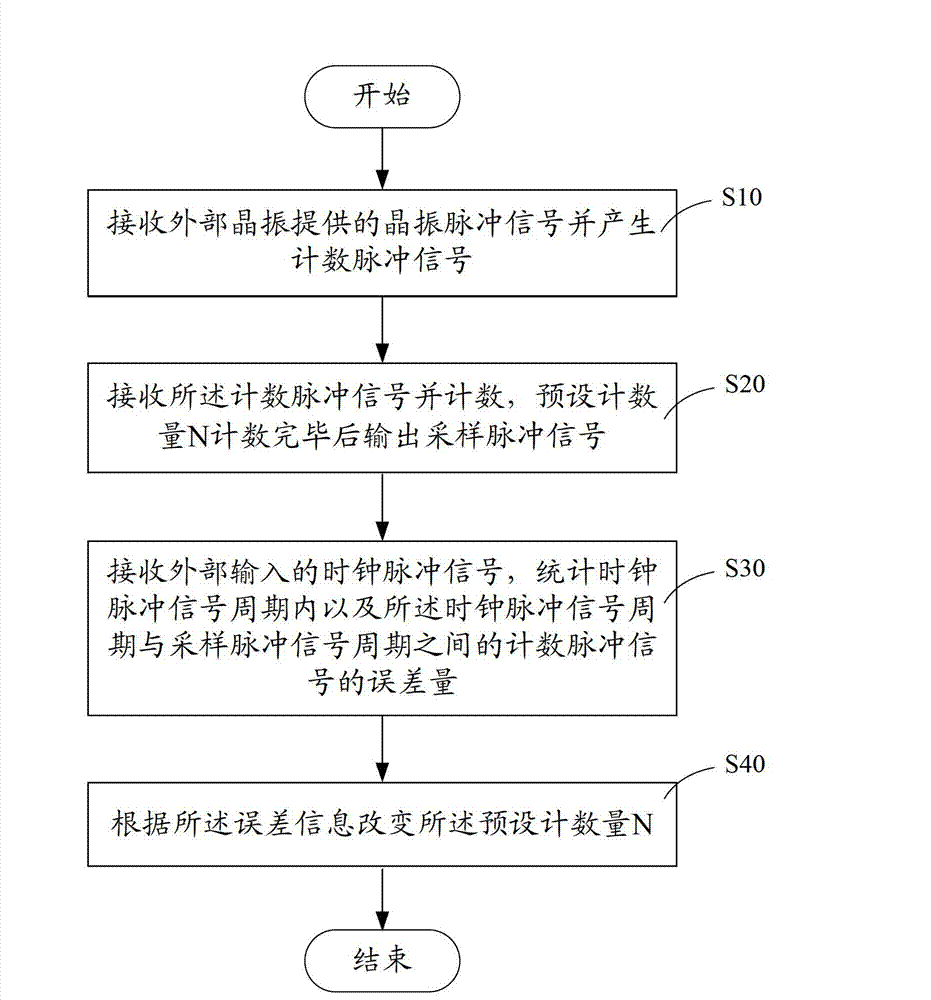

[0030] Such as image 3 As shown, it is a flow chart of a method for realizing sampling clock synchronization in a preferred embodiment. The method for realizing sampling clock synchronization is realized based on a programmable gate circuit integrated chip. In this embodiment, it is mainly implemented in CPLD (Complex Programmable Logic Device, complex programmable logic device) logic chip uses logic circuit design to realize corresponding clock pulse signal comparison, sampling pulse generation, sampling pulse adjustment and other functions, and finally realizes ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More