Device and method for testing performance degradation caused by transistor lattice deformation

The technology of a testing device and testing method, which is applied in the field of microelectronics, can solve problems such as inaccurate calculation of transistor lattice deformation, uneven stress on transistors, uneven stress on chips, etc., to overcome the difficulties of chip bending test methods, The effect of overcoming the limited range of mechanical stress and improving the range of mechanical stress

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

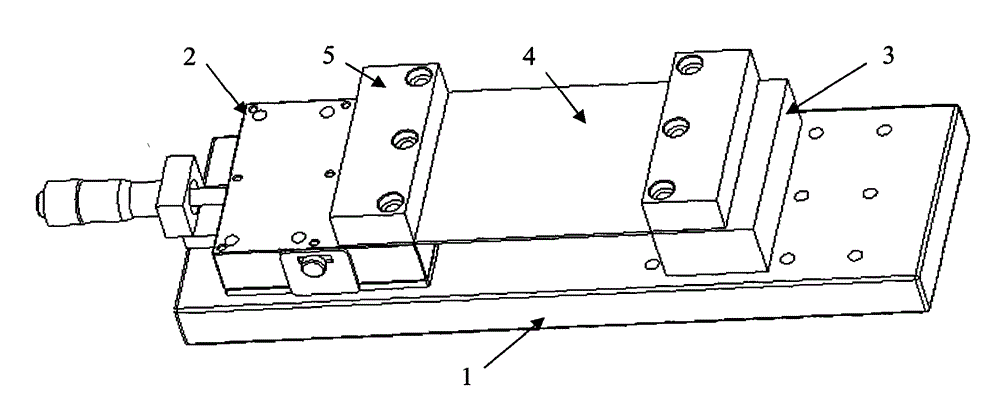

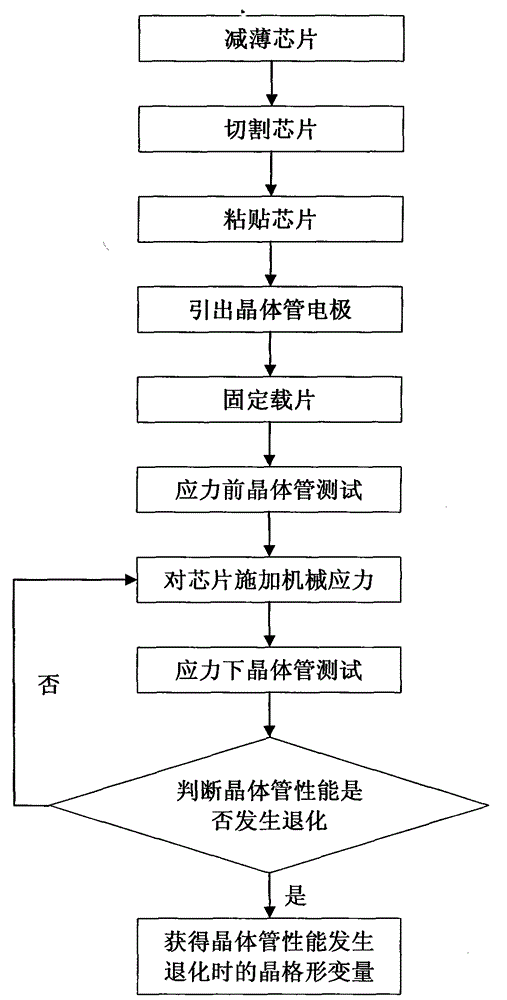

[0035] Refer to attached figure 1 , a test device for performance degradation caused by transistor lattice deformation, including five parts: 1 is a base, 2 is a precision displacement platform, 3 is a spacer, 4 is a carrier, and 5 is a pressing block. in,

[0036]The cuboid base 1 is located at the bottom of the device, and one end is provided with two rows and two columns of four screw holes, which are connected with the precision displacement platform 2 on it with screws; the other end is provided with four rows and three columns of twelve screw holes. When the invention fixes the spacer 3, it can be connected with the spacer 3 on it with screws through one row of screw holes according to the specific lattice deformation test requirements. In the embodiment of the present invention, the spacer 3 is fixed on a row of screw holes on the side closest to the precise displacement platform 2 with screws.

[0037] The precision displacement platform 2 is located on the upper lef...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More