Universal debugging interface-based SoC (System on Chip) hardware debugger

A debugging interface and hardware debugging technology, which is applied in the detection of faulty computer hardware, function inspection, etc., can solve problems such as waste of resources, inability to unify, and slow debugging speed, and achieve the effect of improving performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The present invention will be described in further detail below in conjunction with the accompanying drawings, which are explanations rather than limitations of the present invention.

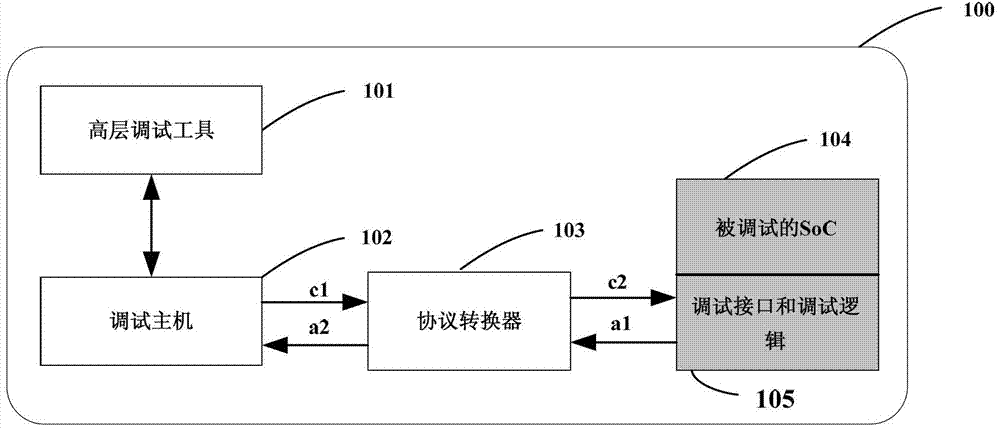

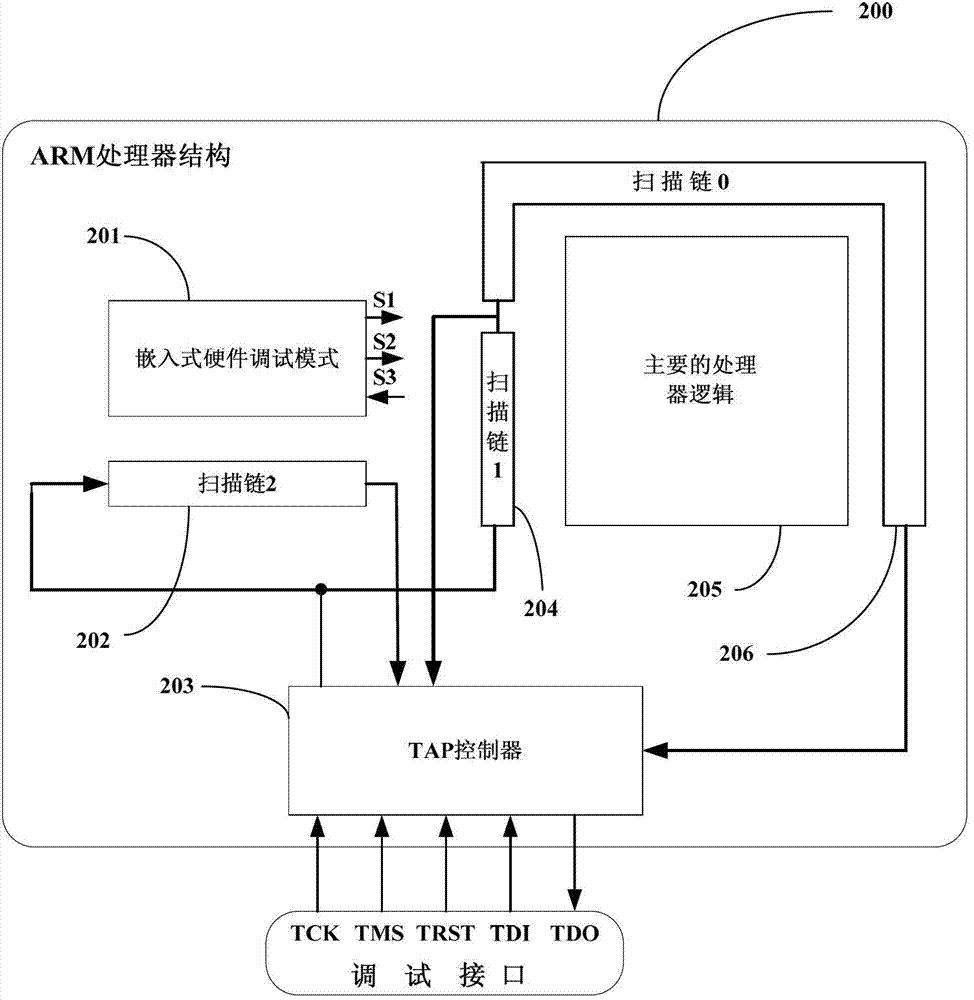

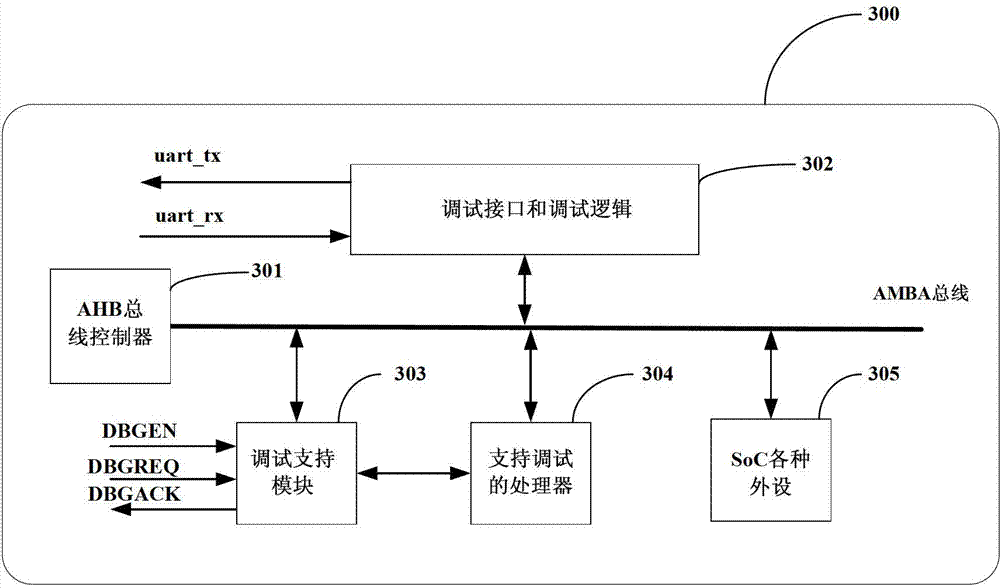

[0049] A SoC hardware debugger based on a general debugging interface, including a general debugging interface, a TAP controller, a scan chain, a debugging control register module, a synchronization module, a JTAG-AHB protocol conversion module, an AHB-DMA module, an AHB bus controller, a debugging Support modules, SoC peripheral modules, and debug-enabled processors;

[0050] The general debugging interface is connected to an external debugging device, and the debugging information is updated to the debugging control register module through the scan chain controlled by the TAP controller;

[0051] The debugging control register module sends the debugging information to the JTAG-AHB protocol conversion module through the synchronization module; the debugging control register module and t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More