Modeling method for PSP mismatch model of MOS transistor

A technology of MOS transistor and mismatch model, which is applied in the fields of instrumentation, calculation, electrical and digital data processing, etc., can solve the problem of less research on MOSFET process fluctuation model, and achieve the effect of high accuracy and clear physical meaning.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further elaborated below in conjunction with the accompanying drawings and examples. The following examples do not limit the present invention. Without departing from the spirit and scope of the inventive concept, changes and advantages that can be imagined by those skilled in the art are all included in the present invention.

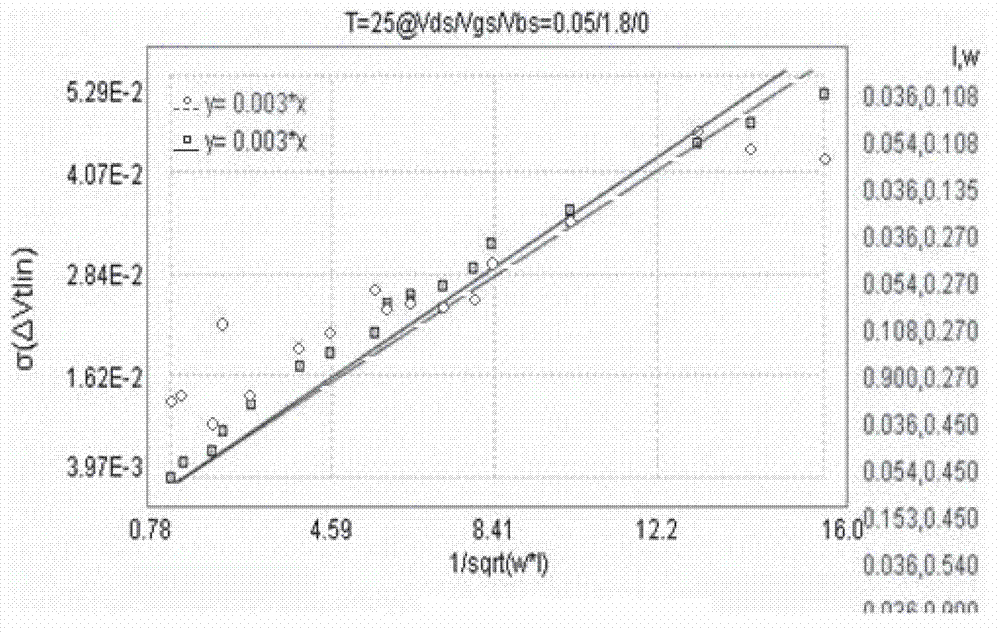

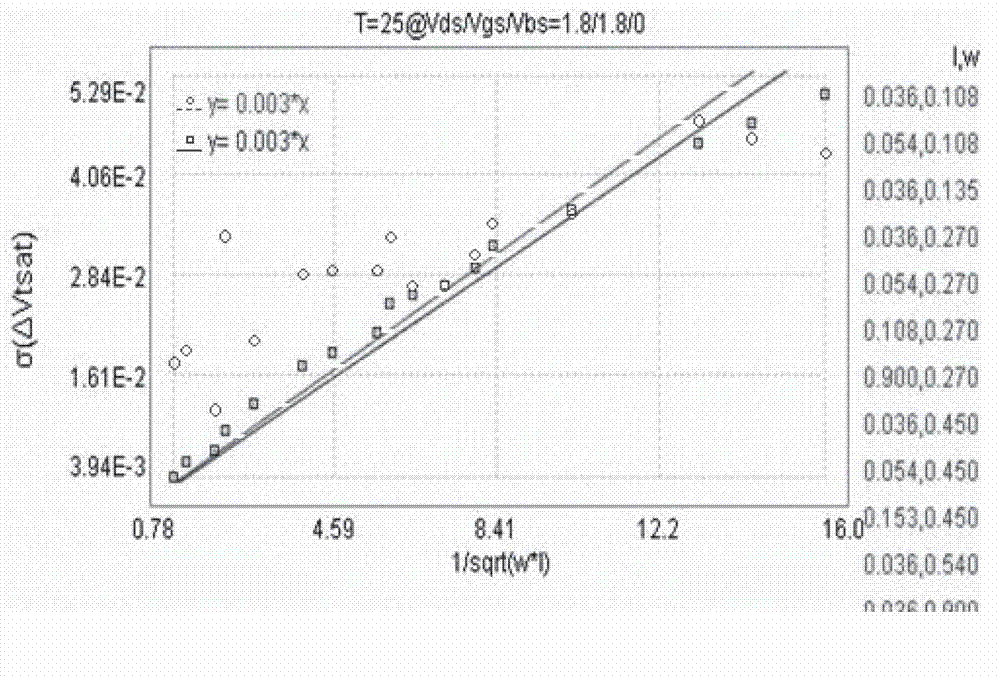

[0039] The invention provides a modeling method of a PSP mismatch model of a MOS transistor, specifically a modeling method of a PSP mismatch model related to a mismatch between a 22nm-130nm standard process MOSFET and device performance. The model established by this method has clear physical meaning and high accuracy, and accurately considers the differences in device electrical characteristics caused by process fluctuations, which is helpful for more accurate simulation of the electrical characteristics of MOSFETs of different sizes and types.

[0040] The method of the invention adds a device performance mismatc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More