Methods of forming non-planar transistors

A transistor and non-planar technology, applied in the field of fabricating non-planar transistor structures, can solve the problems of complex structure, difficulty and high manufacturing difficulty, and achieve the effect of simple process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to enable those skilled in the art of the present invention to further understand the present invention, several preferred embodiments of the present invention are enumerated below, together with the accompanying drawings, to describe in detail the composition and desired effects of the present invention.

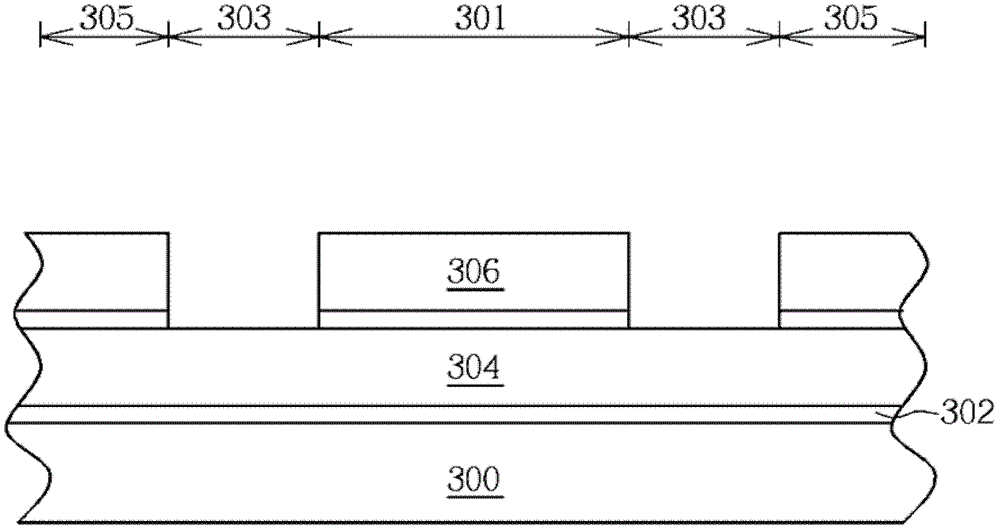

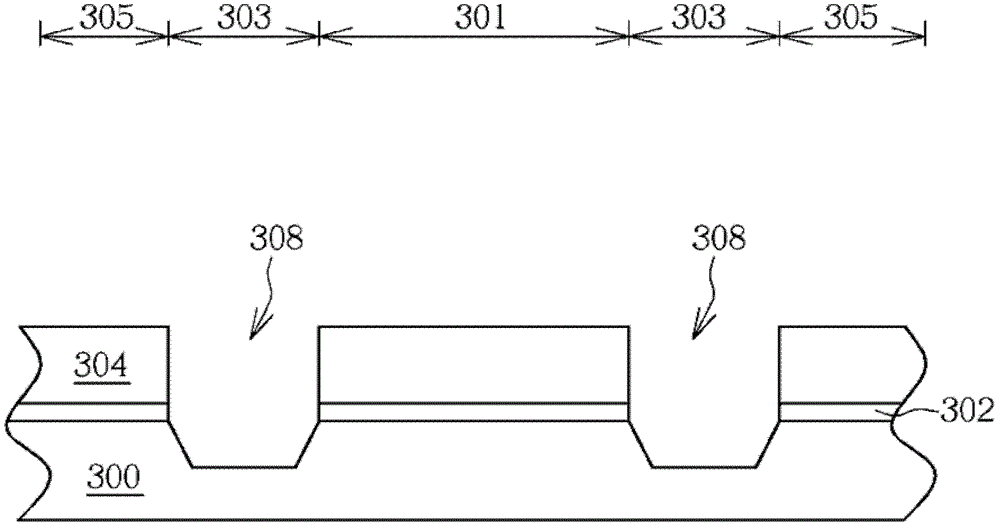

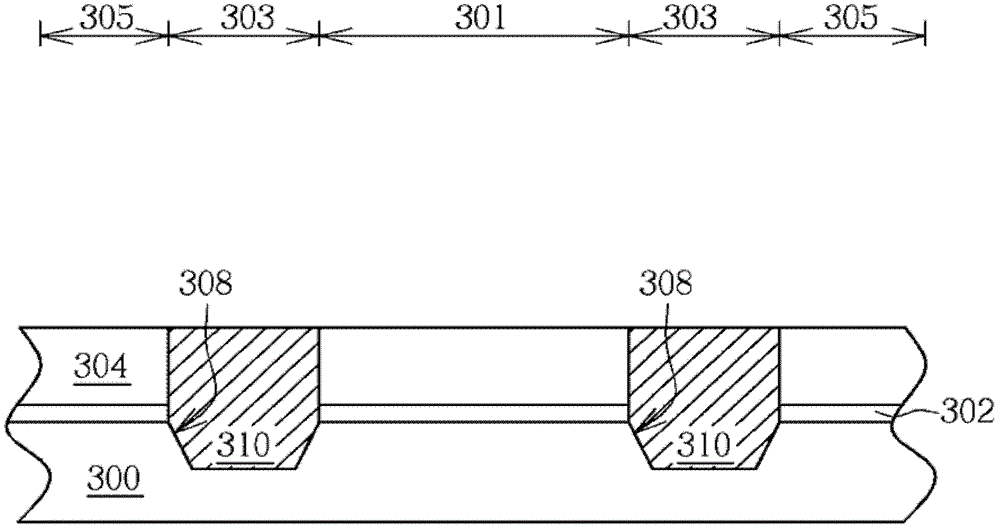

[0020] Please refer to Figure 1 to Figure 10 , is a schematic diagram of the steps of forming a non-planar transistor according to the present invention. Such as figure 1 As shown, a substrate 300 is provided first, and the substrate 300 may be a silicon substrate, an epitaxial silicon substrate, a silicon germanium substrate, a silicon carbide substrate or a silicon-on-insulator (silicon on insulator) -on-insulator, SOI) substrate, etc., but not limited to the above. An active region 301 , an isolation region 303 surrounding the active region 301 , and a peripheral region 305 are defined on the substrate 300 . The active region 301 is a region for produ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More