Non-planar semiconductor structure and process for same

A semiconductor and non-planar technology, which is applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of limited epitaxial layer total volume, metal silicide is not easy to adhere, and cannot be bonded, so as to increase the volume, Ease of adhesion, effect of increasing surface area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

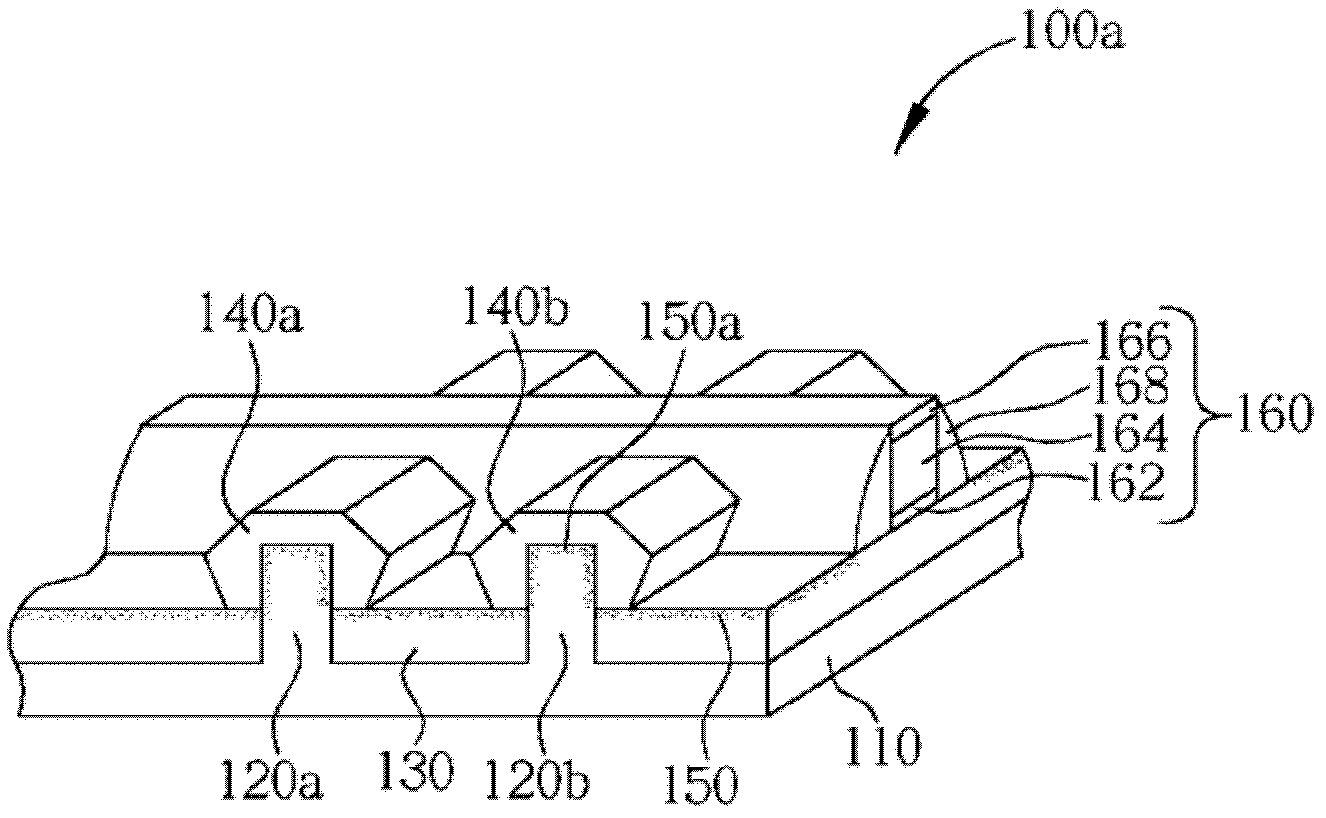

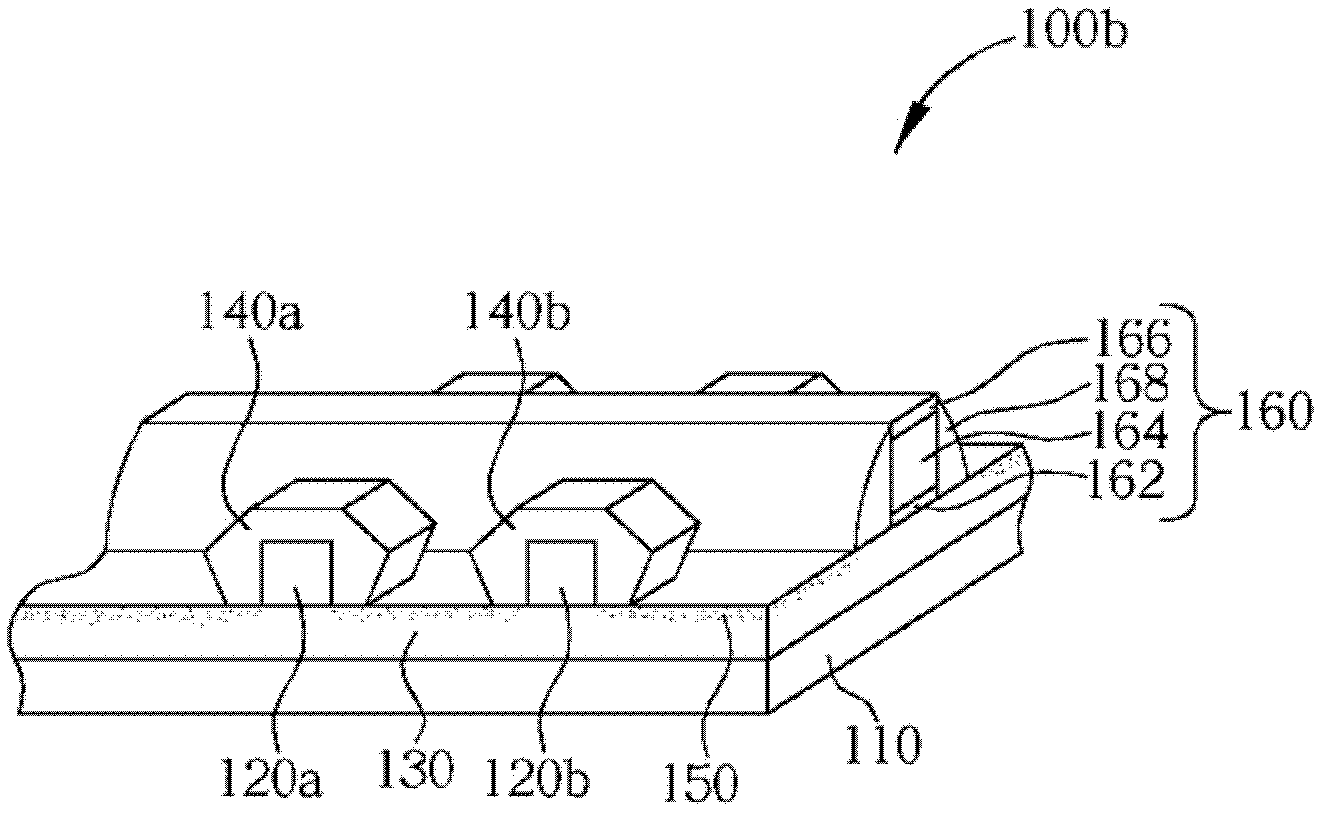

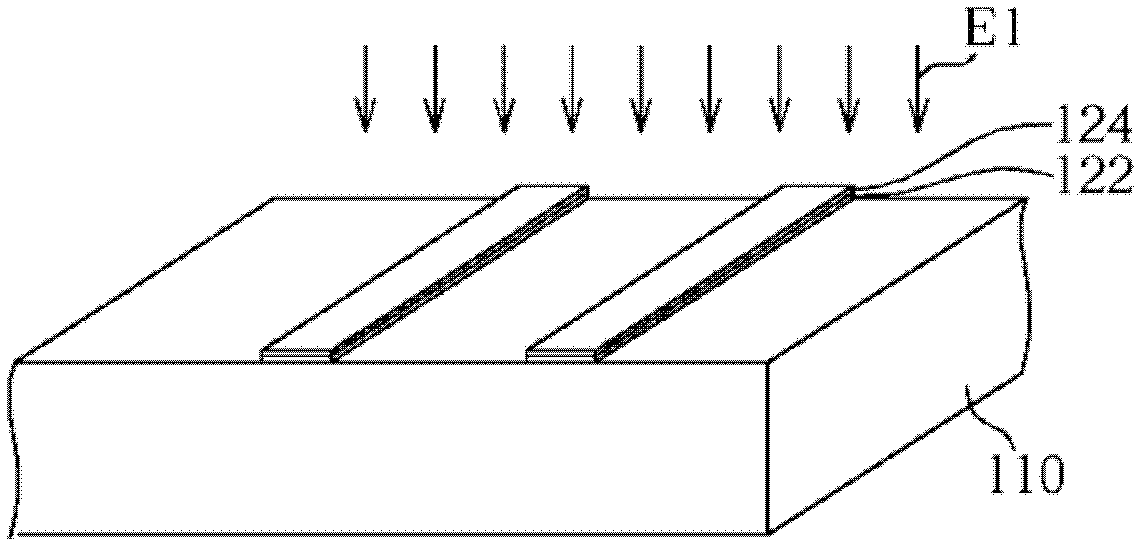

[0024] figure 1 A schematic cross-sectional view of a semiconductor structure containing a silicon substrate according to an embodiment of the present invention is shown. figure 2 A schematic cross-sectional view of a semiconductor structure including a silicon-on-insulator substrate according to another embodiment of the present invention is shown. see Figure 1-2 Both the semiconductor structures 100a and 100b include a substrate 110, two fin structures 120a and 120b, an insulating structure 130, and two epitaxial layers 140a and 140b. The fin structures 120 a and 120 b are located on the substrate 110 . The insulating structure 130 is located between the fin structures 120a and 120b. The insulating structure 130 has a nitrogen-containing layer 150 . The epitaxial layers 140 a and 140 b respectively cover part of the fin structures 120 a and 120 b and are located on the nitrogen-containing layer 150 . Figure 1-2 Only two fin structures 120a and 120b are shown, but the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More