HPI (Host Port Interface) bus upper computer interface based on FPGA (Field Programmable Gate Array)

A bus and interface technology, applied in the field of FPGA implementation of the HPI bus host computer interface, to achieve the effects of reducing complexity, high flexibility, and improving integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] The present invention will be further described below in conjunction with accompanying drawing and specific embodiment:

[0042] The localization of a certain type of aircraft radar warning equipment involves radar signal sorting technology, and the DSP+FPGA method is adopted in the hardware design: the Spartan-3 series FPGA (model XC3S1500) of Xilinx Company is used to collect radar signals, and the TMS320C64X series of TI Company is used DSP (model TMS320C6416) implements the sorting algorithm of radar signals. The HPI bus is the command and data transmission path between FPGA and DSP. As the upper computer of the HPI bus, the FPGA needs to have the interface function of the upper computer of the HPI bus in addition to the radar signal acquisition function. This function uses Verilog HDL in the FPGA. accomplish.

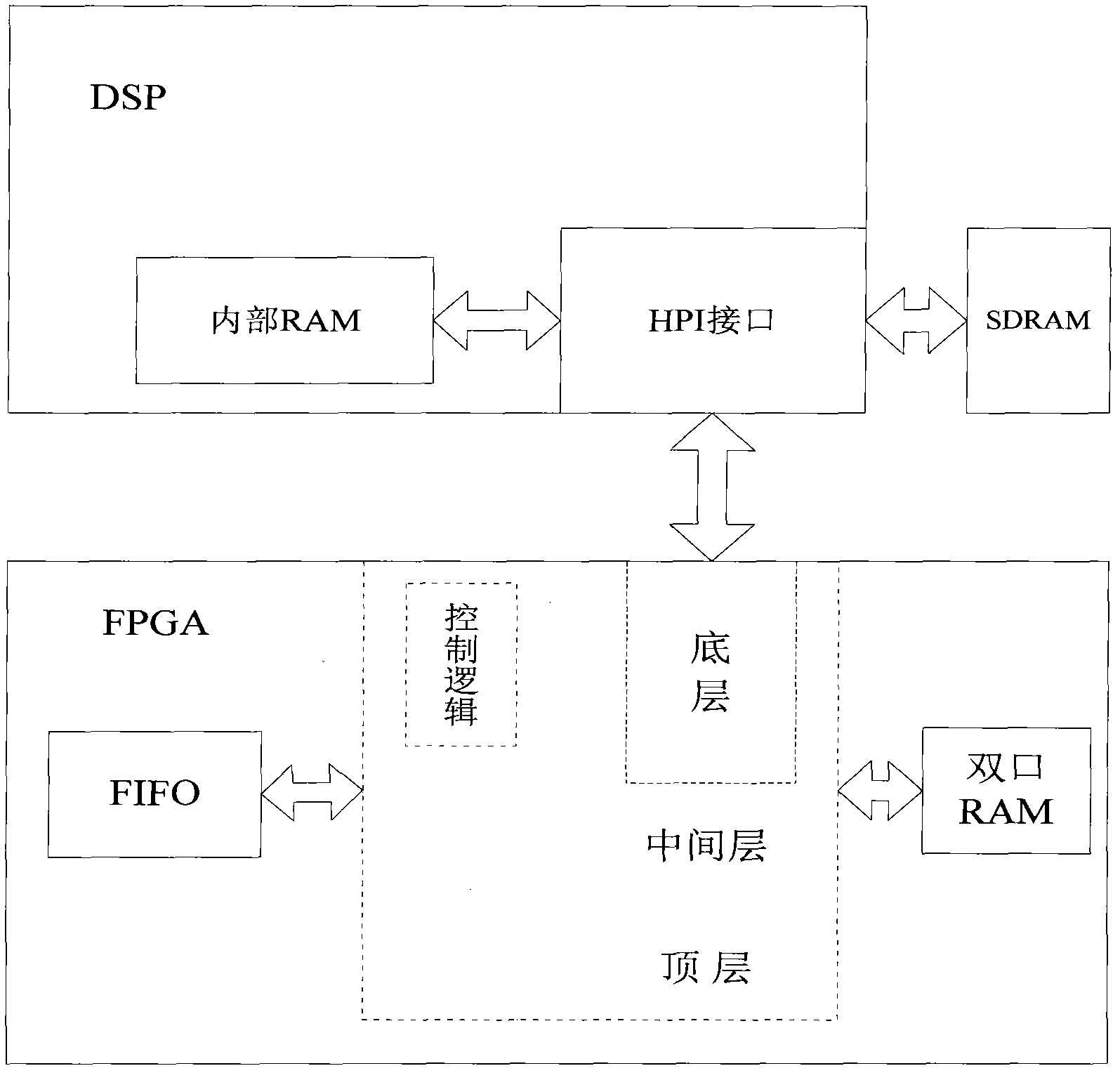

[0043] The system block diagram of the present invention is as figure 1 Shown:

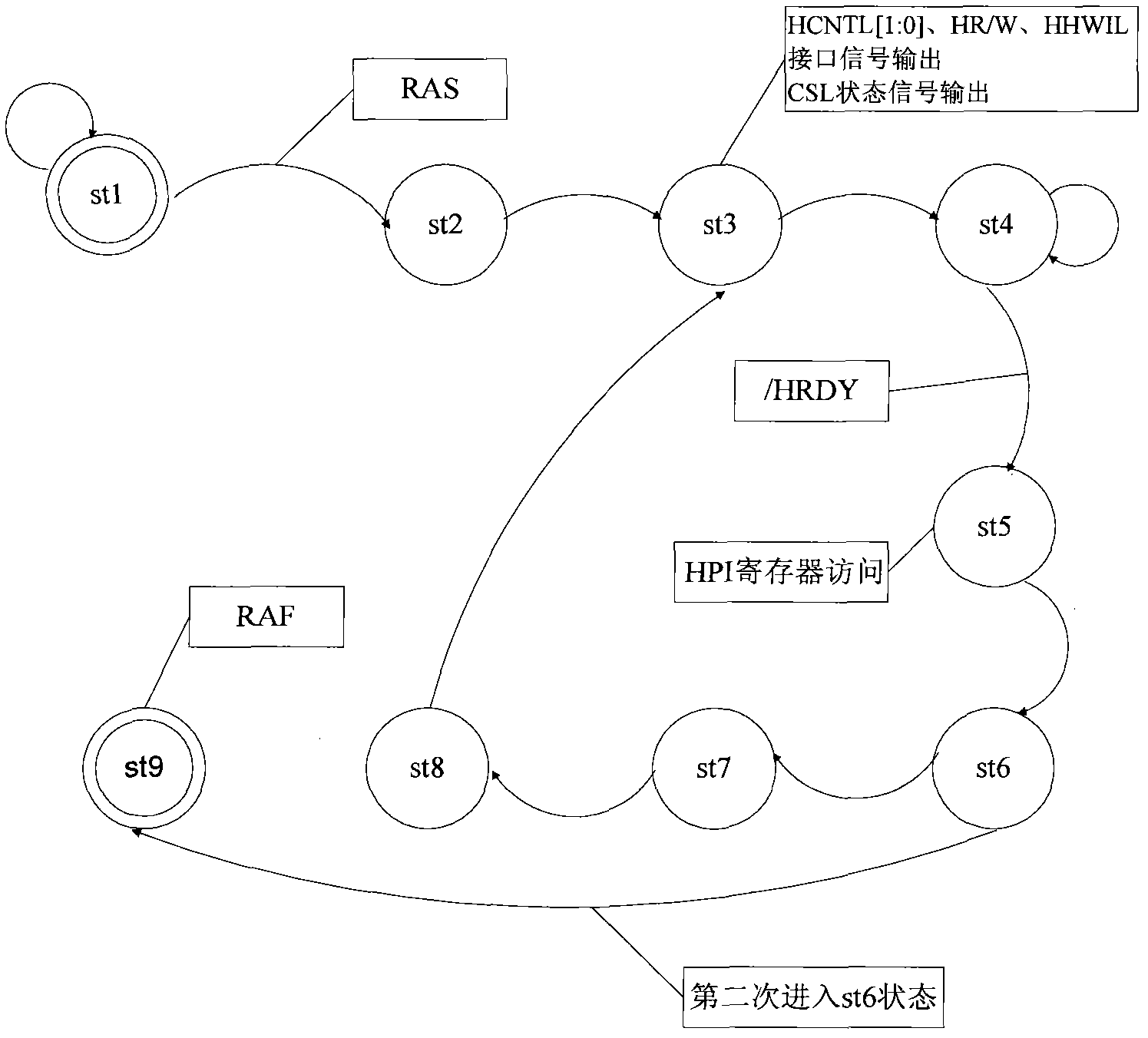

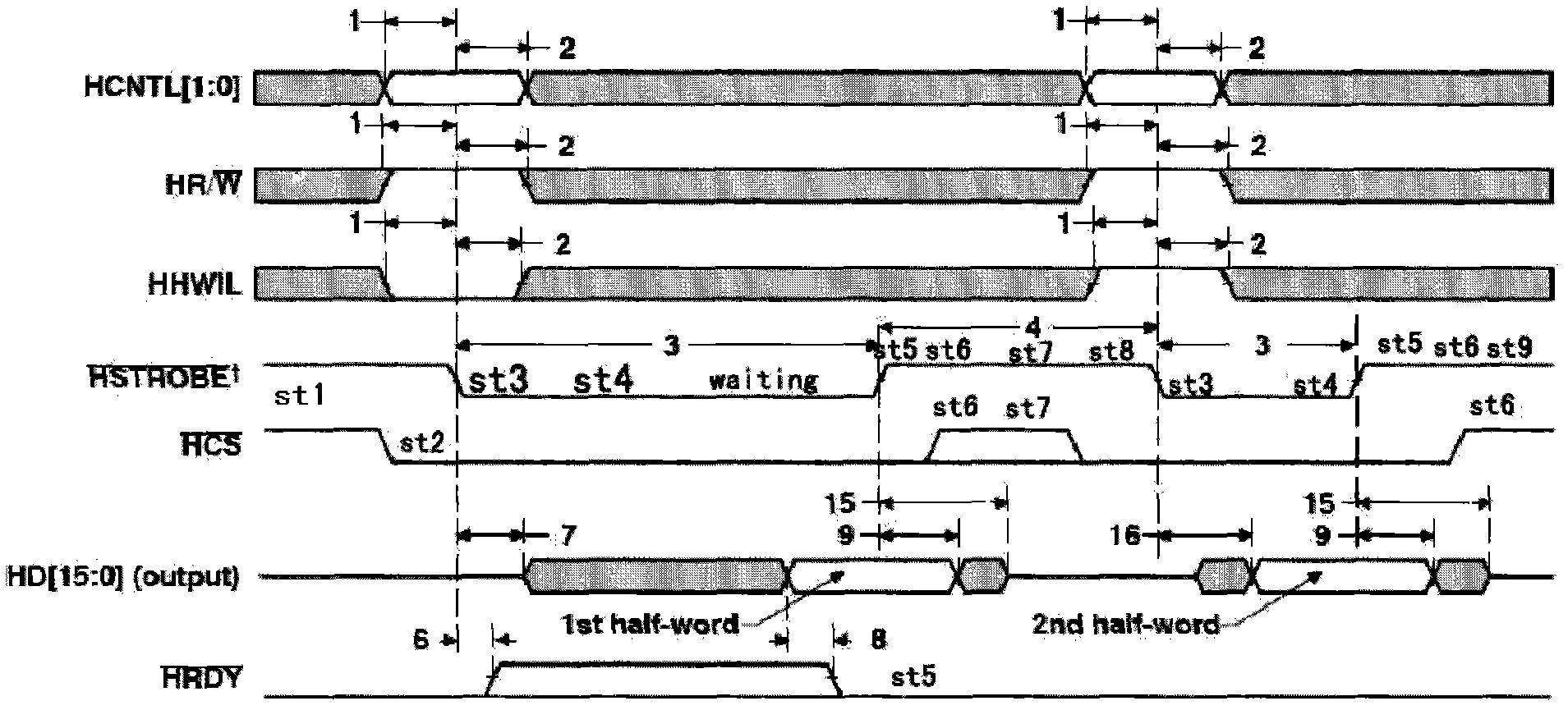

[0044] The host computer interface implementation of the HPI bus can be ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More