Pixel compensating circuit

A compensation circuit and pixel technology, applied in static indicators, instruments, etc., can solve problems such as different brightness, different threshold voltage, and scan time affecting compensation effects, etc., to achieve extended service life, uniform brightness, and overcome process differences and current Falling effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] In order to make the technical content disclosed in this application more detailed and complete, reference may be made to the drawings and the following various specific embodiments of the present invention, and the same symbols in the drawings represent the same or similar components. However, those skilled in the art should understand that the examples provided below are not intended to limit the scope of the present invention. In addition, the drawings are only for schematic illustration and are not drawn according to their original scale.

[0030] The specific implementation manners of various aspects of the present invention will be further described in detail below with reference to the accompanying drawings.

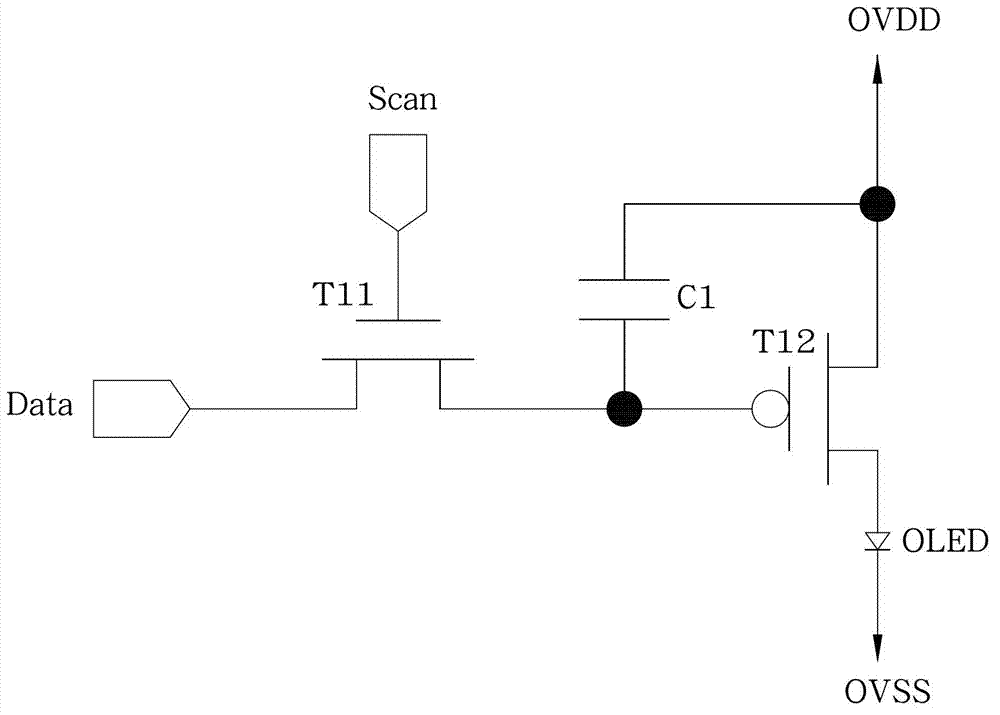

[0031] figure 1 A schematic diagram showing the principle of a pixel compensation circuit using a "2T1C" architecture in the prior art. refer to figure 1 , the pixel compensation circuit is a "2T1C" architecture, where 2T is the thin film transistor T11 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More