Low-voltage operation storage unit circuit of SRAM (Static Random Access Memory)

A storage unit circuit, low-voltage technology, applied in the direction of information storage, static memory, digital memory information, etc., to achieve the effect of reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

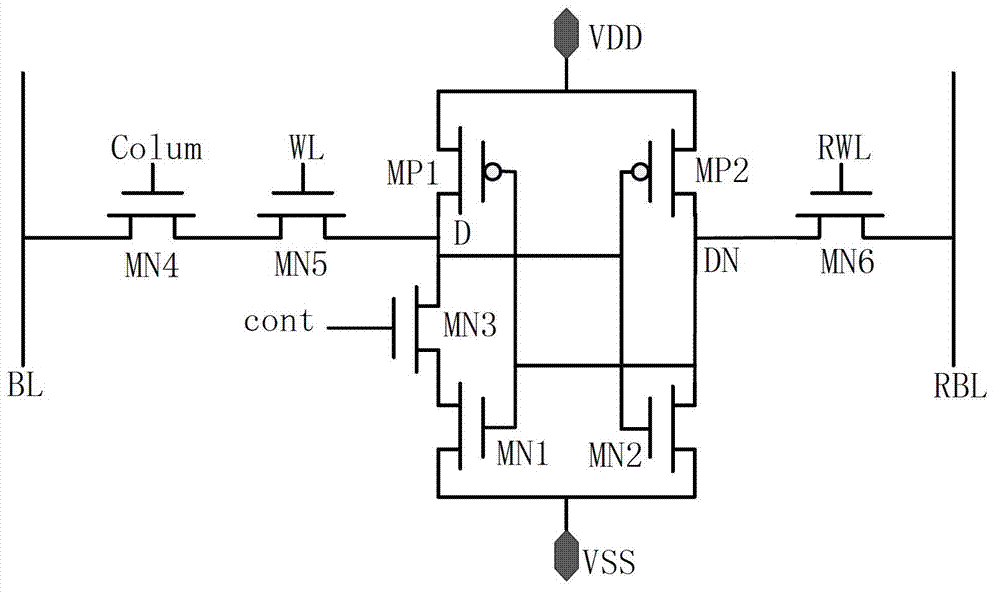

[0016] see figure 1 , The SRAM storage unit circuit with simple structure and low voltage operation of the present invention includes 2 PMOS transistors MP1, MP2 and 6 NMOS transistors MN1-MN6, and the circuit also includes 2 control ports cont and Colum.

[0017] The source end of the MP1 tube is connected to the power supply voltage VDD, and its drain end is connected to the source end of the MN5 tube, the drain end of the MN3 tube, the gate end of the MP2 tube, and the gate end of the MN2 tube, and the gate end is connected to the gate end of the MN1 tube, MN2 tube The drain end of the tube, the drain end of MP2 and the source end of the MN6 tube;

[0018] The source end of the MP2 tube is connected to the power supply voltage VDD;

[0019] The source terminal of the MN1 tube is connected to the ground voltage VSS, and its drain terminal is connected to the source terminal of the MN3 tube; the source terminal of the MN2 tube is connected to VSS; the gate terminal of the MN...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More