Simulation testing system of non-volatile memory (NVM) built-in self-testing circuit

A technology of built-in self-test circuit and simulation test, which is applied in the direction of static memory and instruments, can solve problems such as difficult debugging, failure to automatically detect the integrity of test vectors, and inability to provide test vectors for silicon wafer test machines, so as to ensure integrity The effect of reducing the workload of testing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

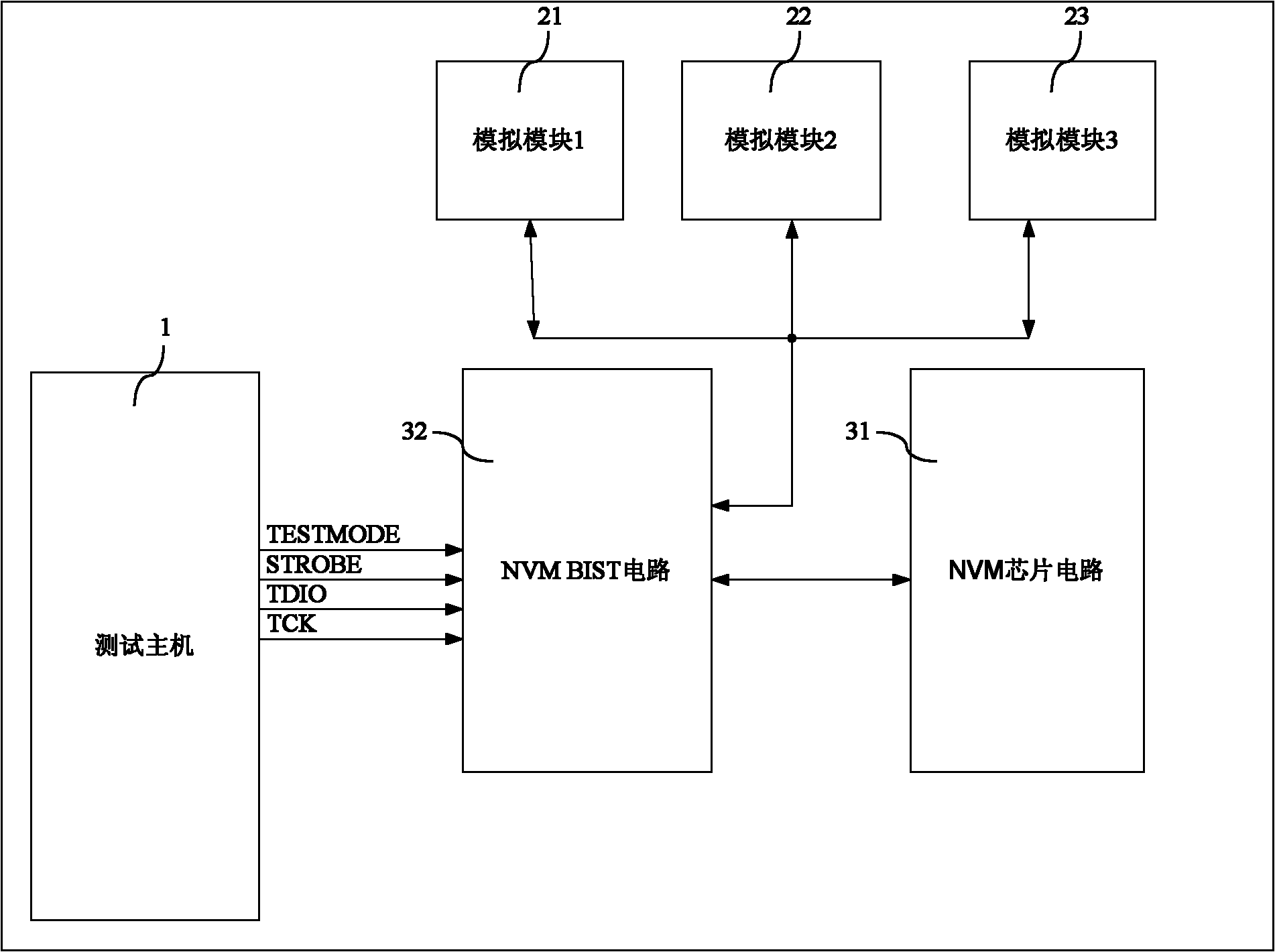

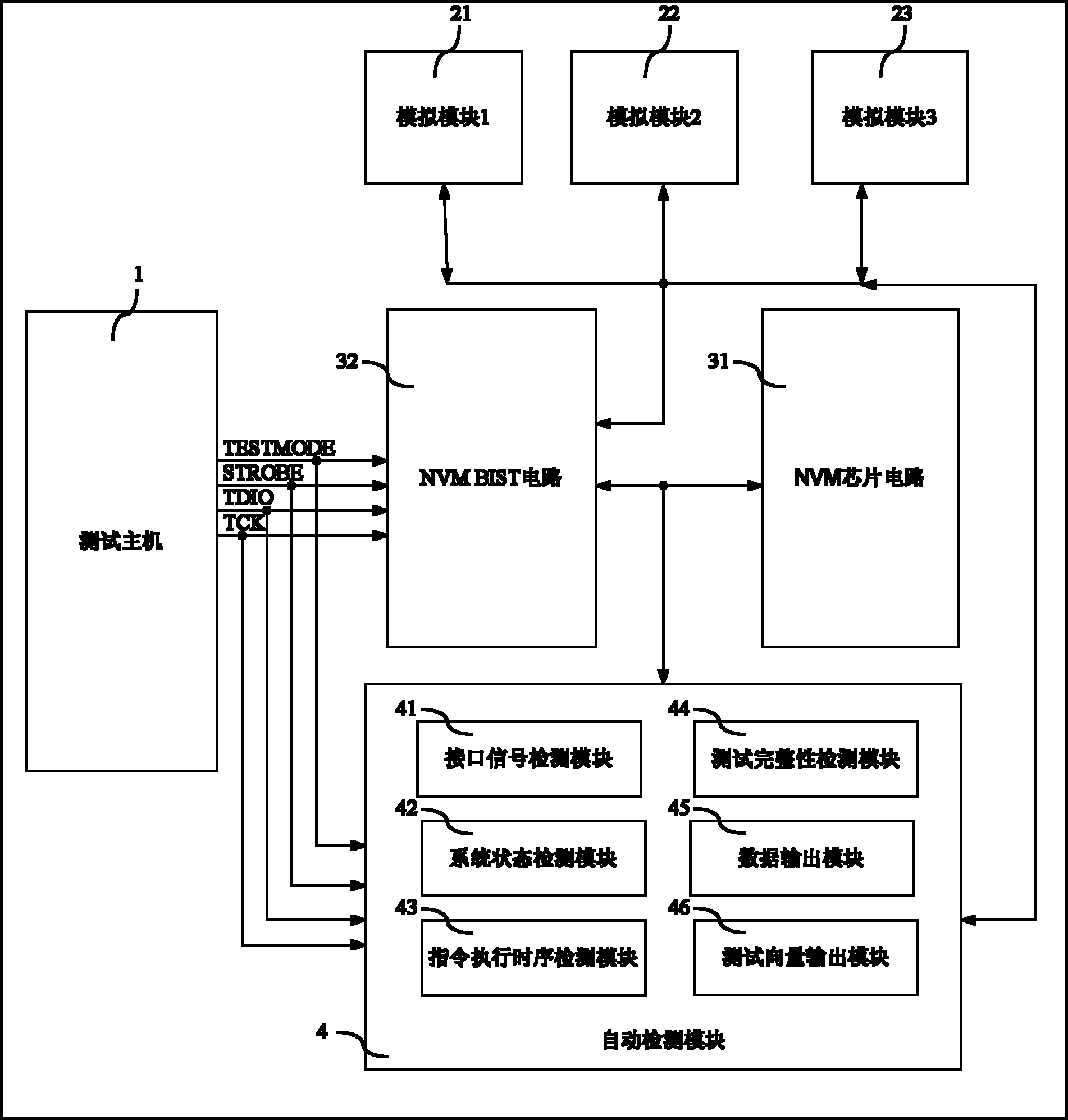

[0029] see figure 2 , which is a simulation test system of a NVM BIST circuit of the present invention. The system includes a test host 1 ; a plurality of analog modules 21 , 22 , 23 , . . . ; an NVM chip circuit 31 ; a BIST circuit 32 of NVM;

[0030] The BIST circuit 32 of the NVM is connected with the test host 1 , each analog module 21 , 22 , 23 , . . . , and the NVM chip circuit 31 . The test host 1 , a plurality of analog modules 21 , 22 , 23 , . . . and the NVM chip circuit 31 constitute the normal working environment of the BIST circuit 32 of the NVM.

[0031] The automatic detection module 4 is connected with the test host 1 , each analog module 21 , 22 , 23 , . . . , the NVM chip circuit 31 , and the BIST circuit 32 of the NVM. The automatic detection module 4 detects the connected modules, realizes data detection and timing detection, and can analyze and locate related problems.

[0032] Described automatic detection module 4 specifically comprises:

[0033] - ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More