Packaged semiconductor device and method of packaging the semiconductor device

A technology of semiconductor and semiconductor tube, applied in the field of semiconductor packaging

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The making and using of embodiments of the invention are discussed in detail below. It should be appreciated, however, that the present invention provides many applicable inventive concepts that can be embodied in a wide variety of specific contexts. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention.

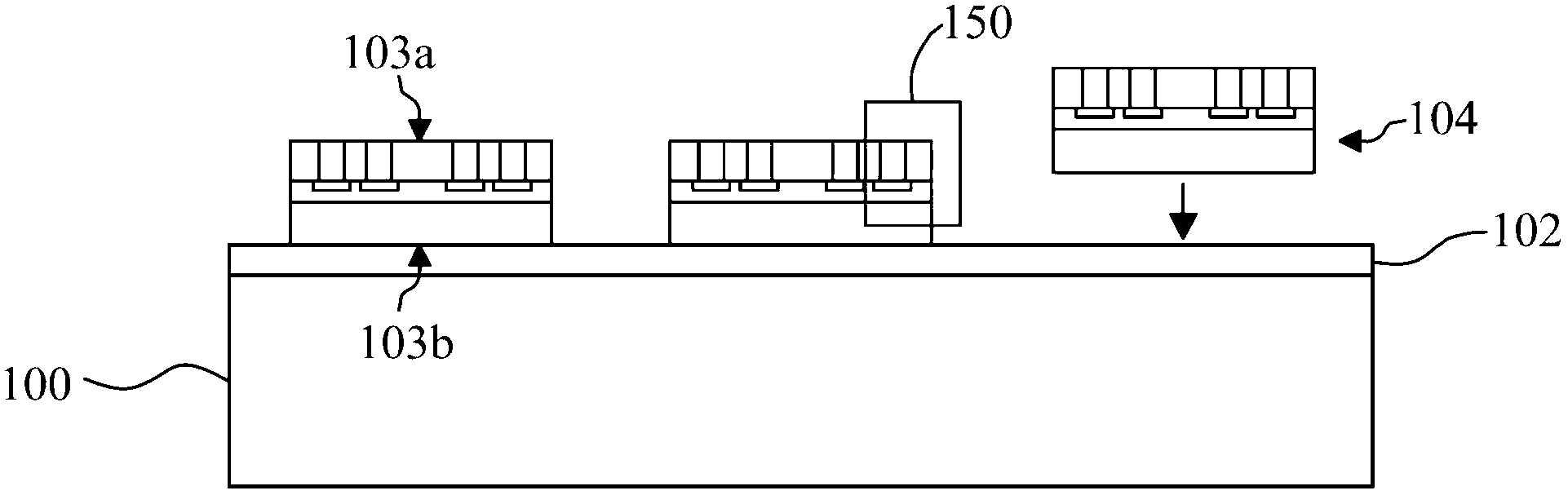

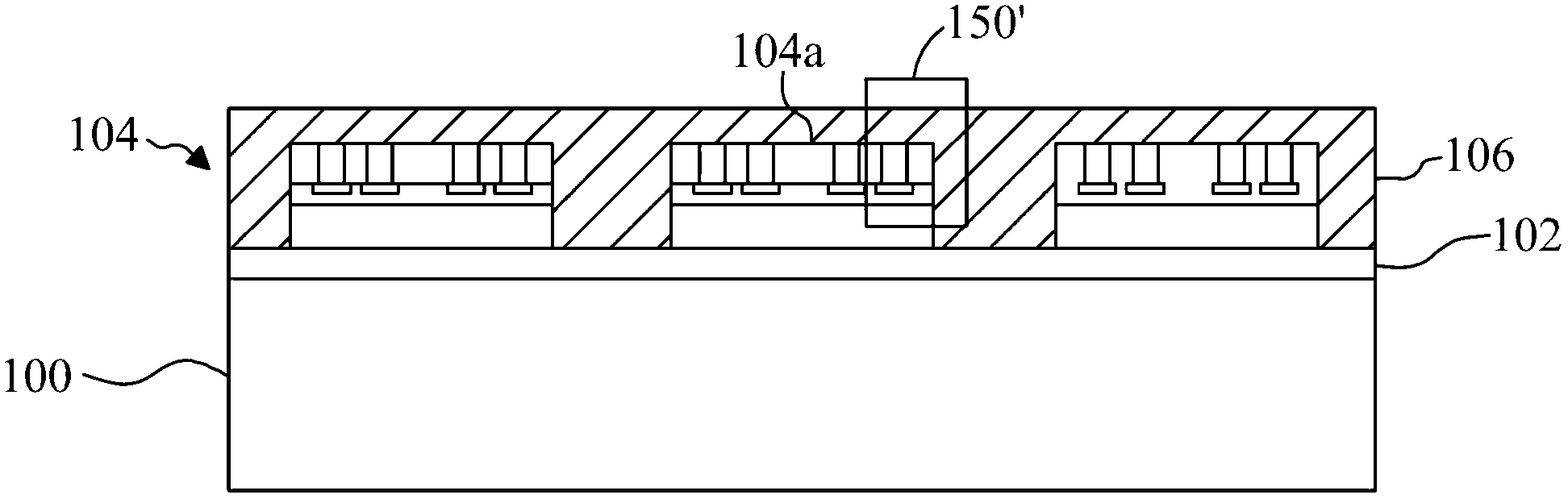

[0038] Figure 1A to Figure 1I are cross-sectional views of a semiconductor device at various packaging stages according to an embodiment of the present invention. first reference Figure 1A , a carrier wafer 100 is provided. As examples, carrier wafer 100 may comprise glass, silicon oxide, aluminum oxide, and the like. The thickness of the carrier wafer 100 may range from about a few mils to tens of mils, and may include a diameter of about 300 mm in some embodiments. The carrier wafer 100 serves as a packaged semiconductor device or die 104 (see Figure 1B ) functi...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More