Flexibly configured field-programmable gate array (FPGA) chip and configuration method thereof

A FAGA, chip technology, applied in sequence/logic controller program control, electrical program control, etc., can solve the problems of inflexible configuration method, uncontrollable configuration process, high configuration and working power consumption, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

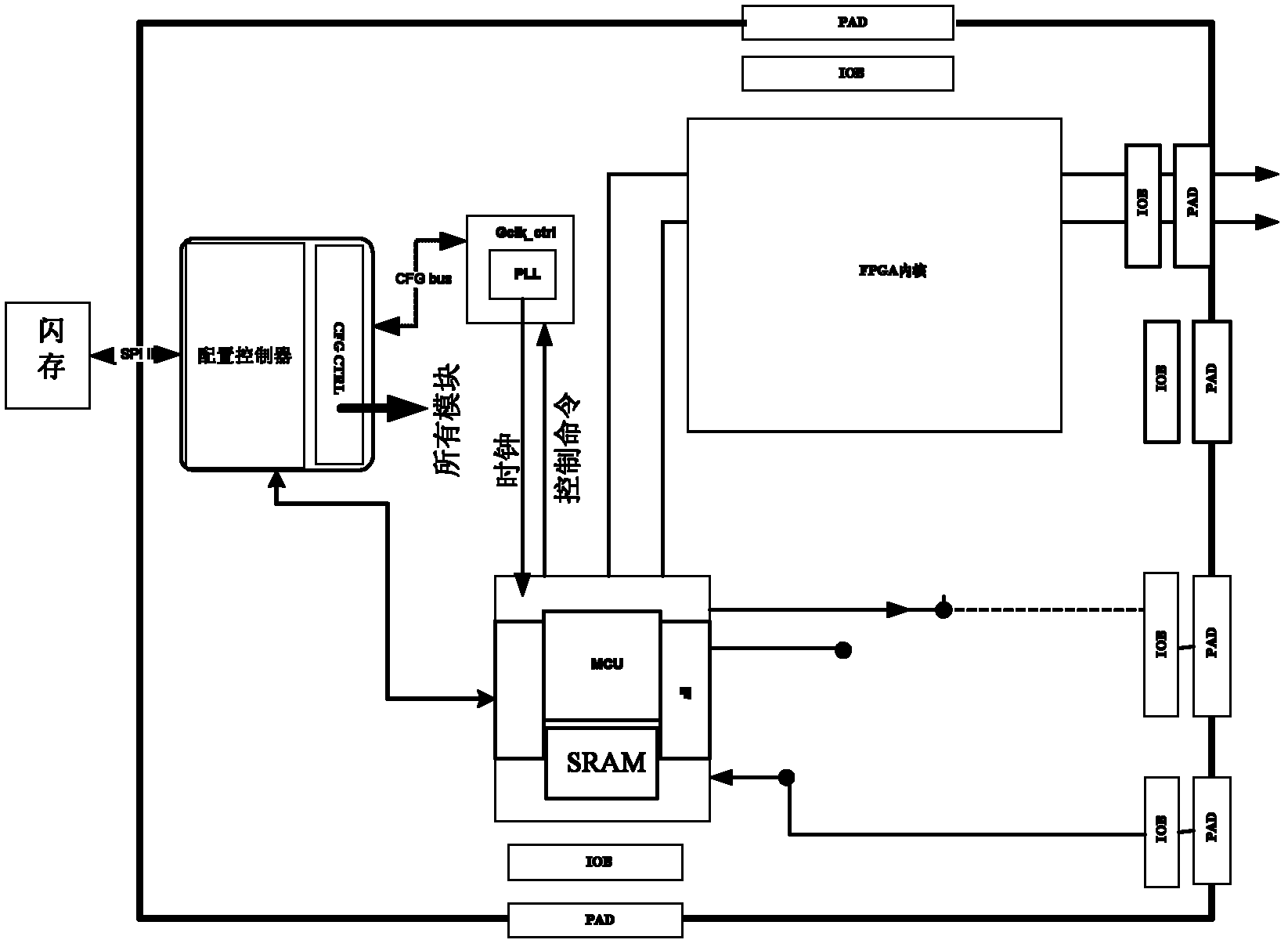

[0018] figure 1 It is a structural diagram of an FPGA chip according to an embodiment of the present invention. Such as figure 1 As shown, the FPGA chip includes several functional modules integrated in the same chip, the FPGA core module, the phase-locked loop module, the configuration controller config controller and the microprocessor MCU. Among them, the MCU is connected with a memory SRAM, which can read user programs or data. Several functional modules include, for example, an input / output unit IOB and the like. The FPGA core module is a specific array that completes the Field Programmable Logic Array. The configuration controller invokes the configuration program stored in the flash memory FLASH under the control of the MCU to configure one or more of the several functional modules of the FPGA chip, the FPGA...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More