Testing shell suitable for on-chip network embedded type IP core

A network-on-chip and embedded technology, applied in the detection of faulty computer hardware, etc., can solve the problems of poor adaptability of other test modes, inapplicability of multicast test mode, no reference to NoC test optimization effect, etc., to reduce transmission The effect of data volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

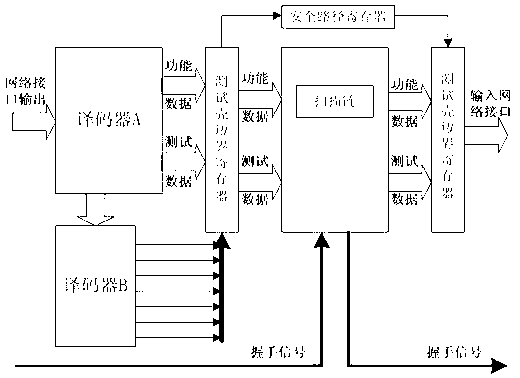

[0023] The technical solution of the invention will be described in detail below in conjunction with the accompanying drawings.

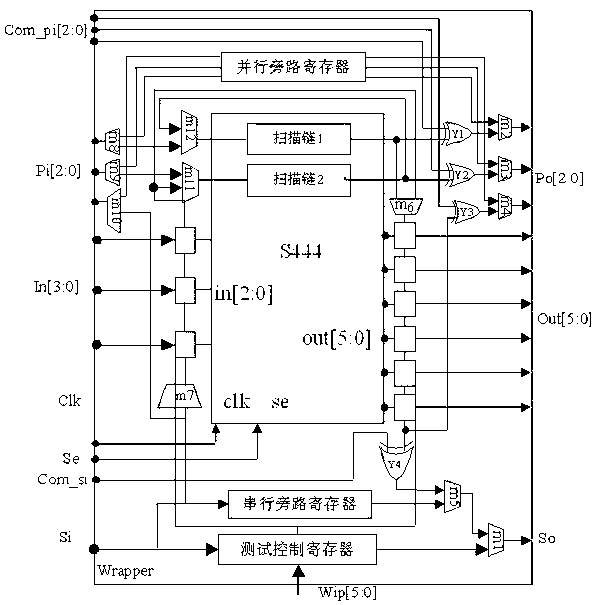

[0024] Taking the S444 circuit in the ISCAS89 reference timing circuit as an example, the circuit realization of each component of the test case, the interface circuit of the test case and the data transmission routes of various test modes are described in detail.

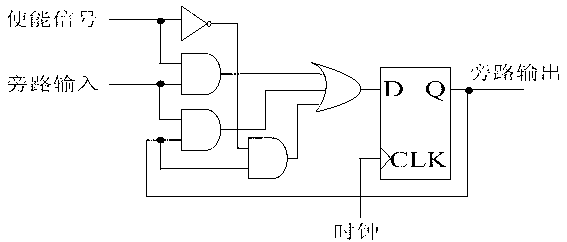

[0025] The S444 core structure after adding the test shell is as follows figure 2 As shown, including parallel input port Pi[2:0], parallel bypass register, parallel output port Po[2:0], serial input port Si, serial bypass register, serial output port So, test control register , a first multiplexer m1 , a serial test response comparator, a parallel test response comparator, a correct test response signal parallel input port Com_pi[2:0], a correct test response signal serial input port Com_si. The input terminal of the parallel bypass register is connected to the parallel input port Pi[...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More