Shift register and drive method thereof

A technology of shift register and driving method, which is applied in the direction of static memory, digital memory information, instruments, etc., can solve the problem of distortion of the output signal of the shift register, and achieve the effect of preventing distortion and improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

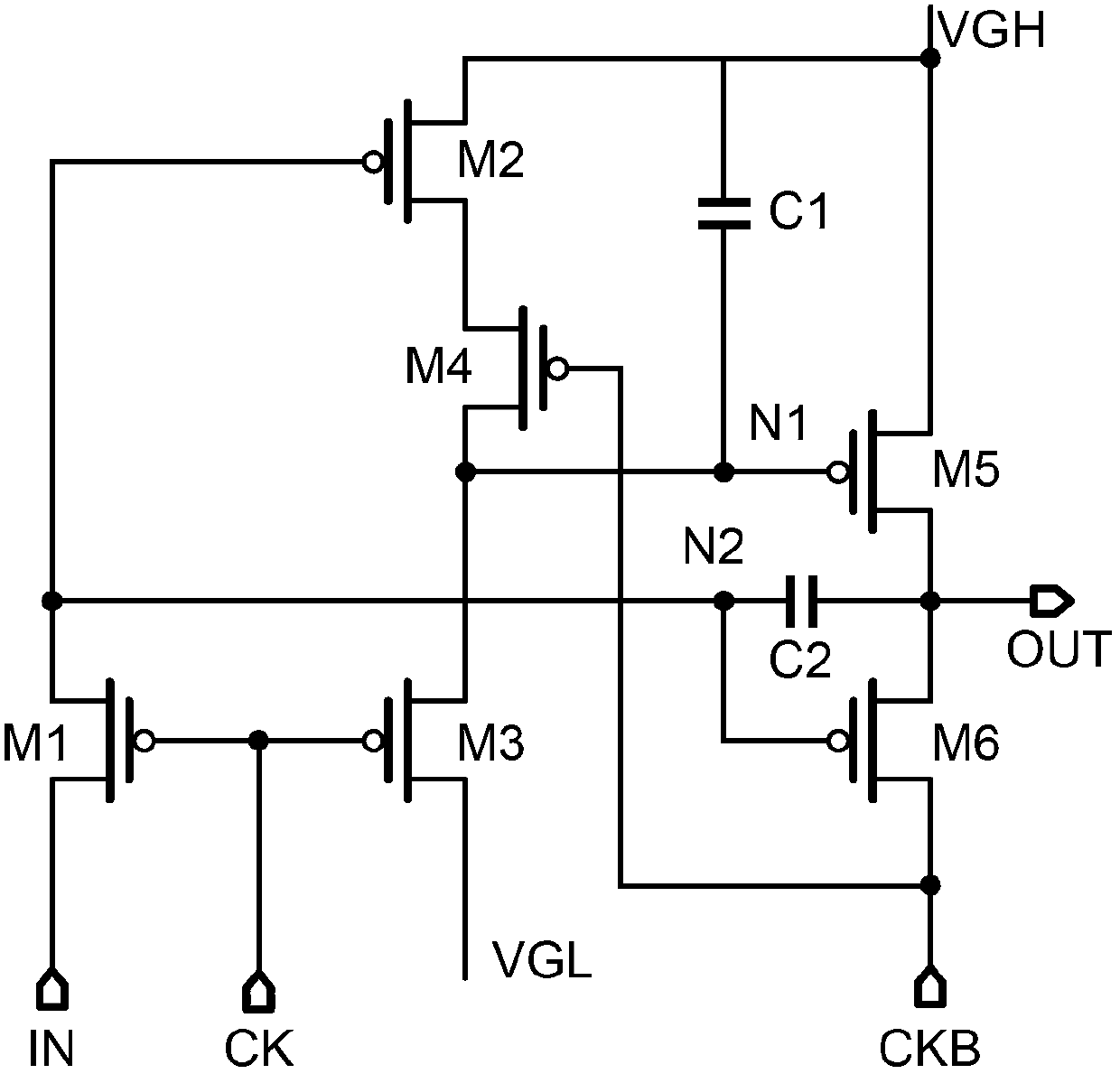

[0037] Please refer to image 3 , which is a schematic structural diagram of a shift register according to an embodiment of the present invention. Such as image 3 As shown, the shift register includes: a first transistor M1, a second transistor M2, a third transistor M3, a fourth transistor M4, and a fifth transistor M5, wherein,

[0038]The gate of the first transistor M1 is connected to the output terminal OUT of the shift register, its drain is connected to the first level signal terminal VGH1, its source is connected to the drain of the second transistor M2 and the fourth transistor M4 the gate connection;

[0039] The gate of the second transistor M2 is connected to the first clock signal terminal CK, and its source is connected to the second level signal terminal VGL1;

[0040] The gate of the third transistor M3 is connected to the first clock signal terminal CK, its source is connected to the input terminal IN of the shift register, and its drain is connected to th...

Embodiment 2

[0058] The difference between the second embodiment and the first embodiment is that for image 3 In the shift register shown, the transistors (the first transistor M1 , the second transistor M2 , the third transistor M3 , the fourth transistor M4 and the fifth transistor M5 ) are NMOS transistors.

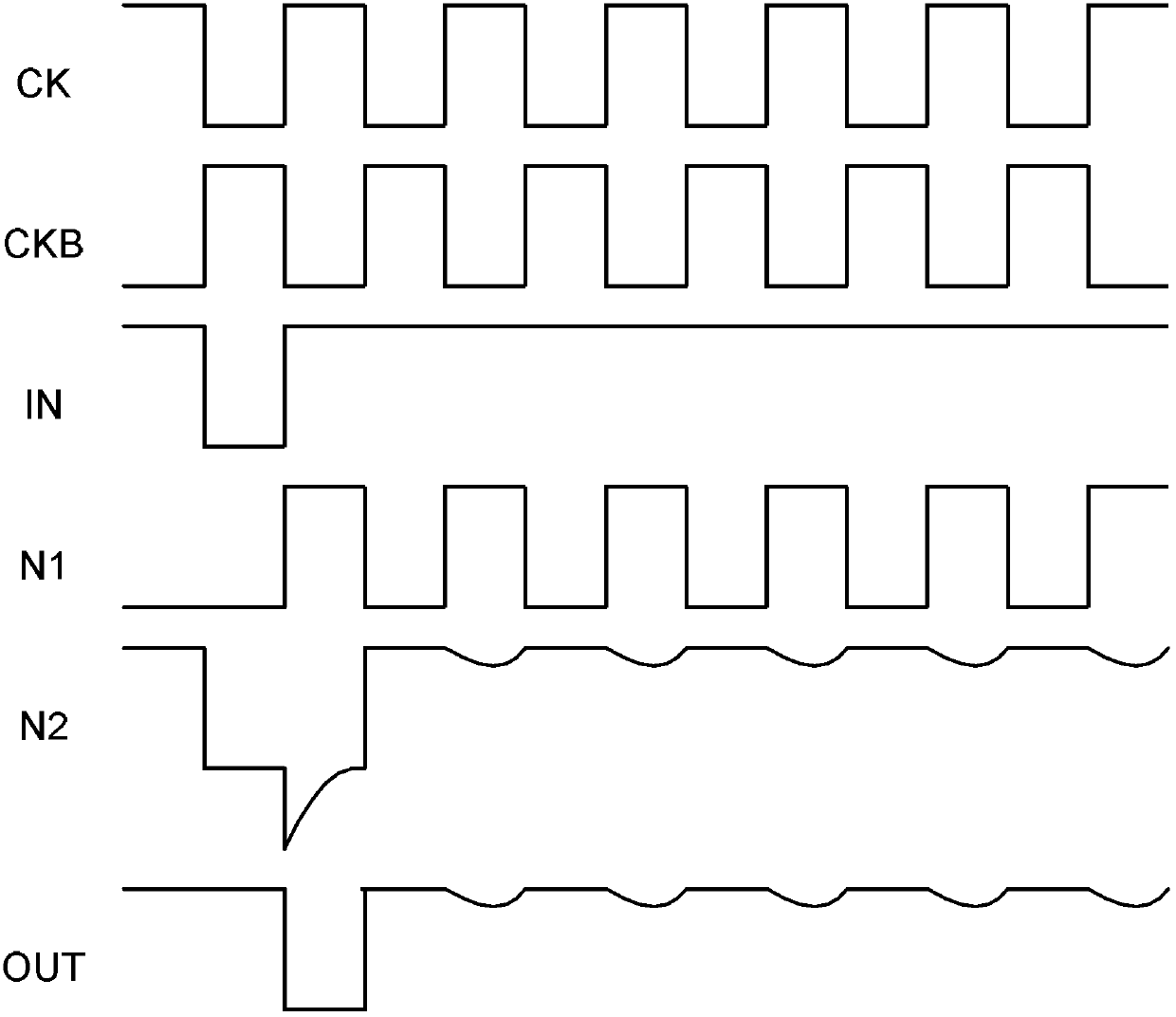

[0059] Among them, the working timing of the shift register please refer to Figure 5 , the input signal of the first level signal terminal VGL2 is a low level signal, the input signal of the second level signal terminal VGH2 is a high level signal, the input terminal IN of the shift register is connected to a high level pulse signal, the first The clock signal terminal CK is connected to the first clock signal ck, and the second clock signal terminal CKB is connected to the second clock signal ckb, wherein the second clock signal ckb is an inverted signal of the first clock signal ck.

[0060] Please continue to refer Figure 5 , specifically, the shift register mainly includes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More