Method for protecting shallow trench isolation regions

A technology of shallow trench isolation region and shallow trench is applied in the field of protection of shallow trench isolation region, which can solve the problems of non-disclosure and the like, and achieve the effects of increasing yield, less modification of process steps, and improved device performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The specific embodiment of the present invention will be further described below in conjunction with accompanying drawing:

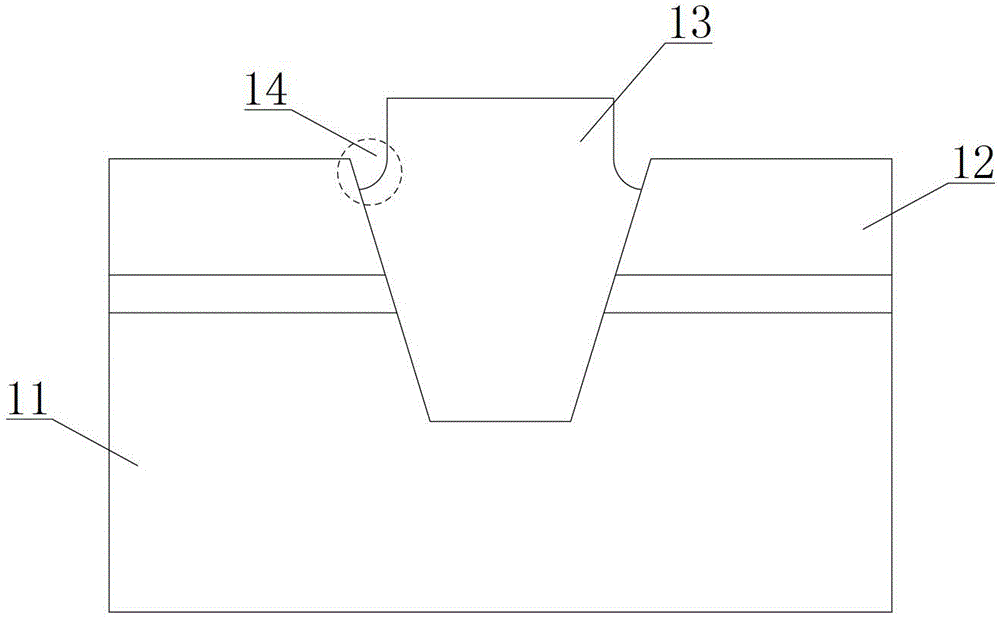

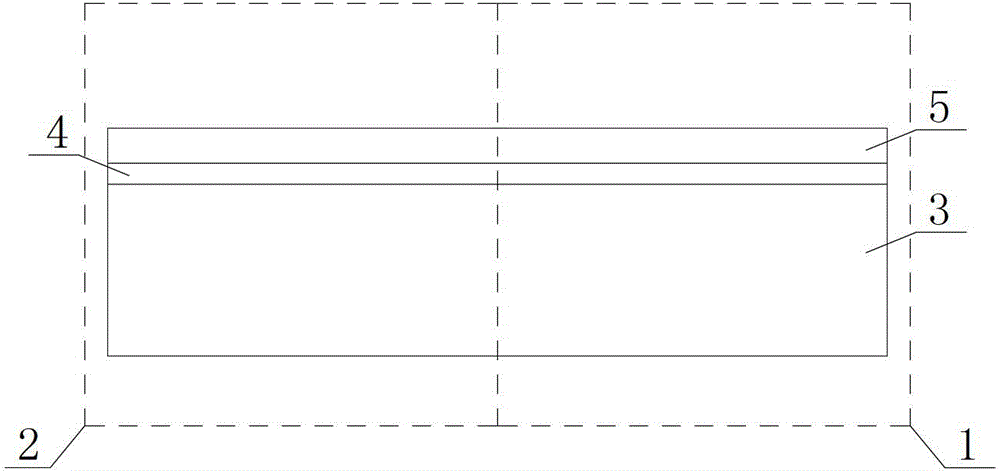

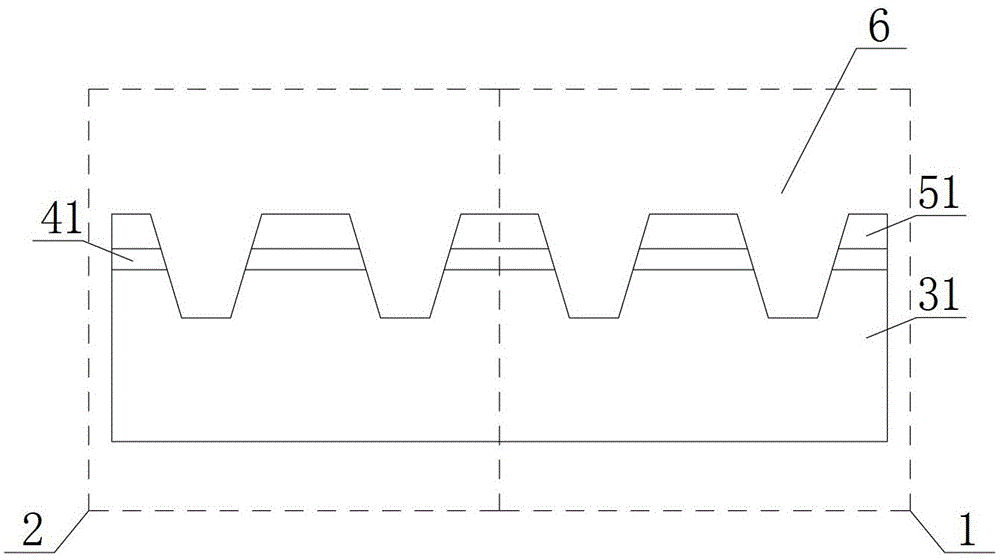

[0030] Figure 2-9 It is a schematic structural flow diagram of an embodiment of the method for protecting shallow trench isolation regions of the present invention; as Figure 2-9 As shown, a method for protecting shallow trench isolation regions is applied in the preparation process of high-voltage devices compatible with low-voltage devices, and specifically includes the following steps:

[0031] Firstly, a substrate 3 having a high-voltage device region 2 and a low-voltage device region 1 is provided, and a thickness of (preferably or etc.) the oxide layer 4 and a thickness of (preferably or etc.) sacrificial nitride layer 5; wherein, the oxide layer 4 covers the upper surface of the substrate 3, and the sacrificial nitride layer 5 covers the upper surface of the oxide layer 4, and then forms such as figure 2 structure shown....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com