Multi-core processor on-chip network system based on FPGA and provided with accelerator

A multi-core processor and network-on-chip technology, which is applied in the fields of electrical digital data processing, instruments, and various digital computer combinations. rate, the effect of reducing the processing time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The present invention will be further described in detail below in combination with specific embodiments. However, it should not be understood that the scope of the above subject matter of the present invention is limited to the following embodiments, and all technologies realized based on the content of the present invention belong to the scope of the present invention.

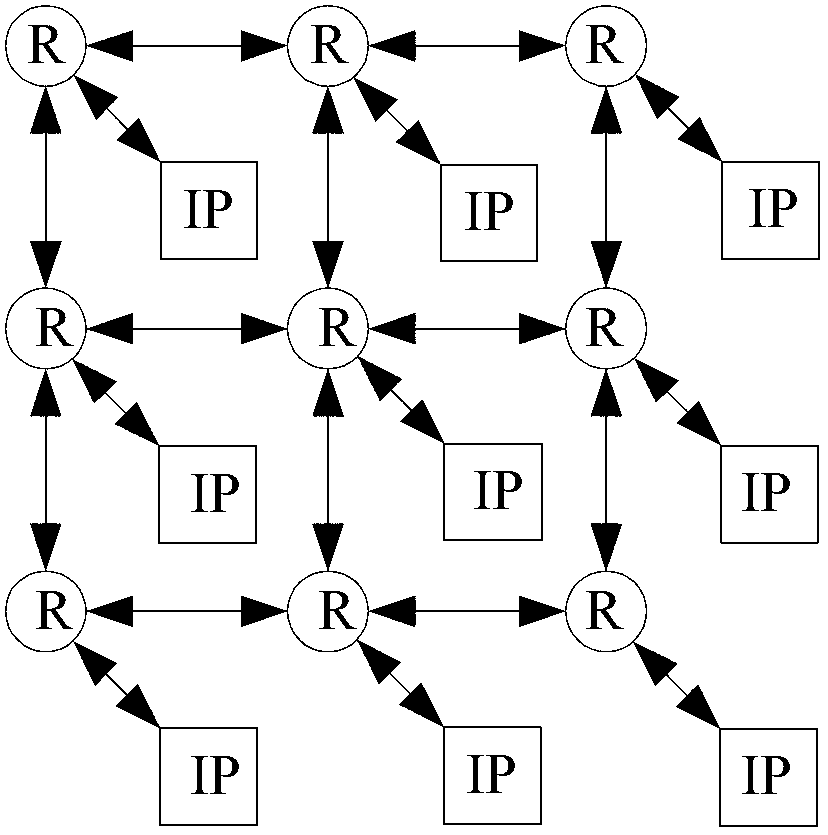

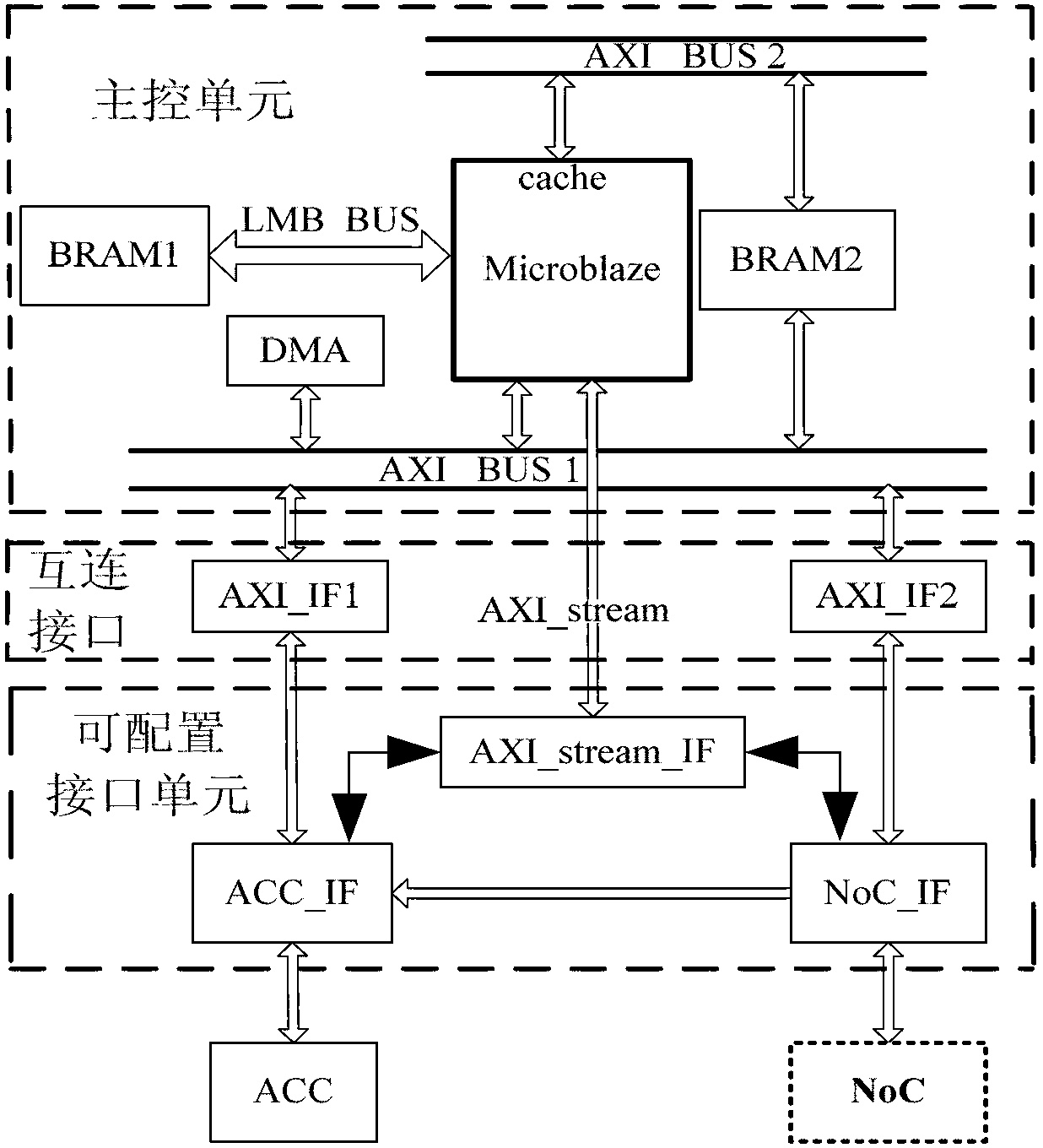

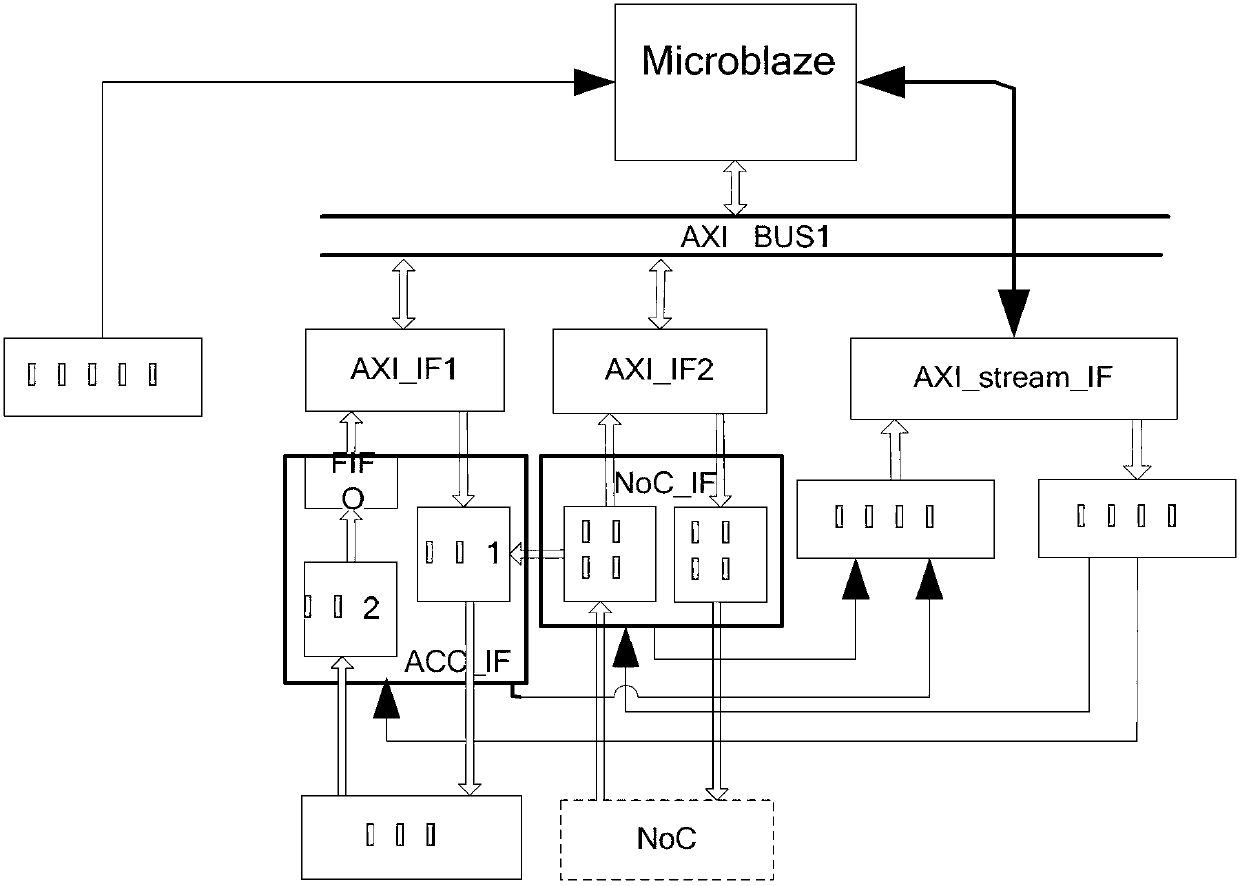

[0027] The system of the present invention is realized on the FPGA chip of Xilinx. In the design, the general-purpose processor core used is Microblaze. The system mainly includes two parts: network on chip and processor node. see figure 1 with figure 2, the FPGA-based multi-core processor on-chip network system with accelerators of the present invention includes a plurality of routing nodes R, communication links between the routing nodes R and adjacent routing nodes R (two-way arrows indicate communication links) To form a network-on-chip NoC, each routing node R is mounted with a processor nod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com