Scan chain trigger capable of tolerating soft errors

A flip-flop, soft error technology, applied in the direction of dynamic coding, etc., can solve problems such as unfavorable ATE testing, complex control timing, etc., to achieve the effects of optimizing control timing, simplifying control timing, and reducing power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] The soft-error tolerant scan chain flip-flop proposed by the present invention will be described in detail below with reference to the drawings and embodiments.

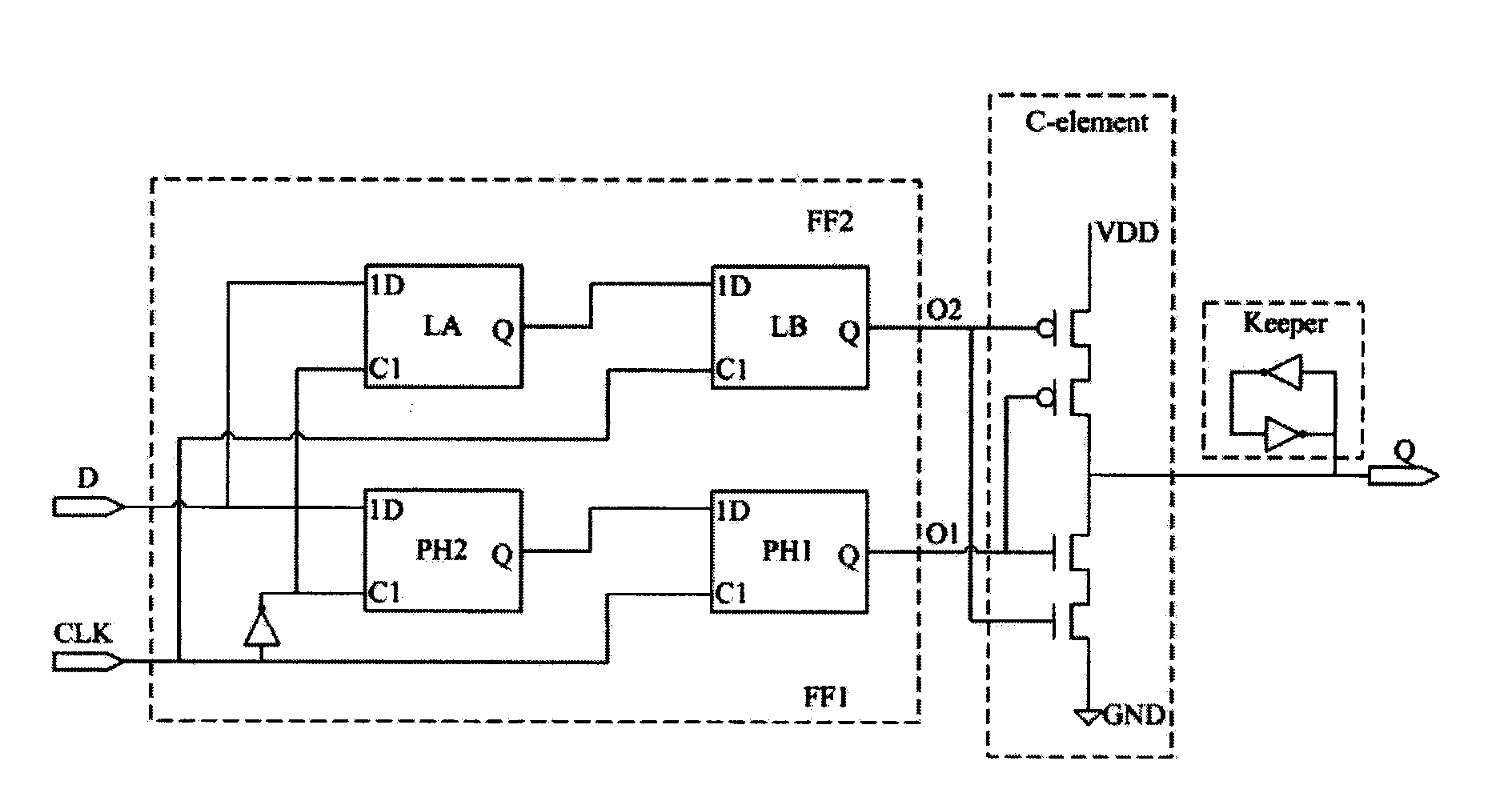

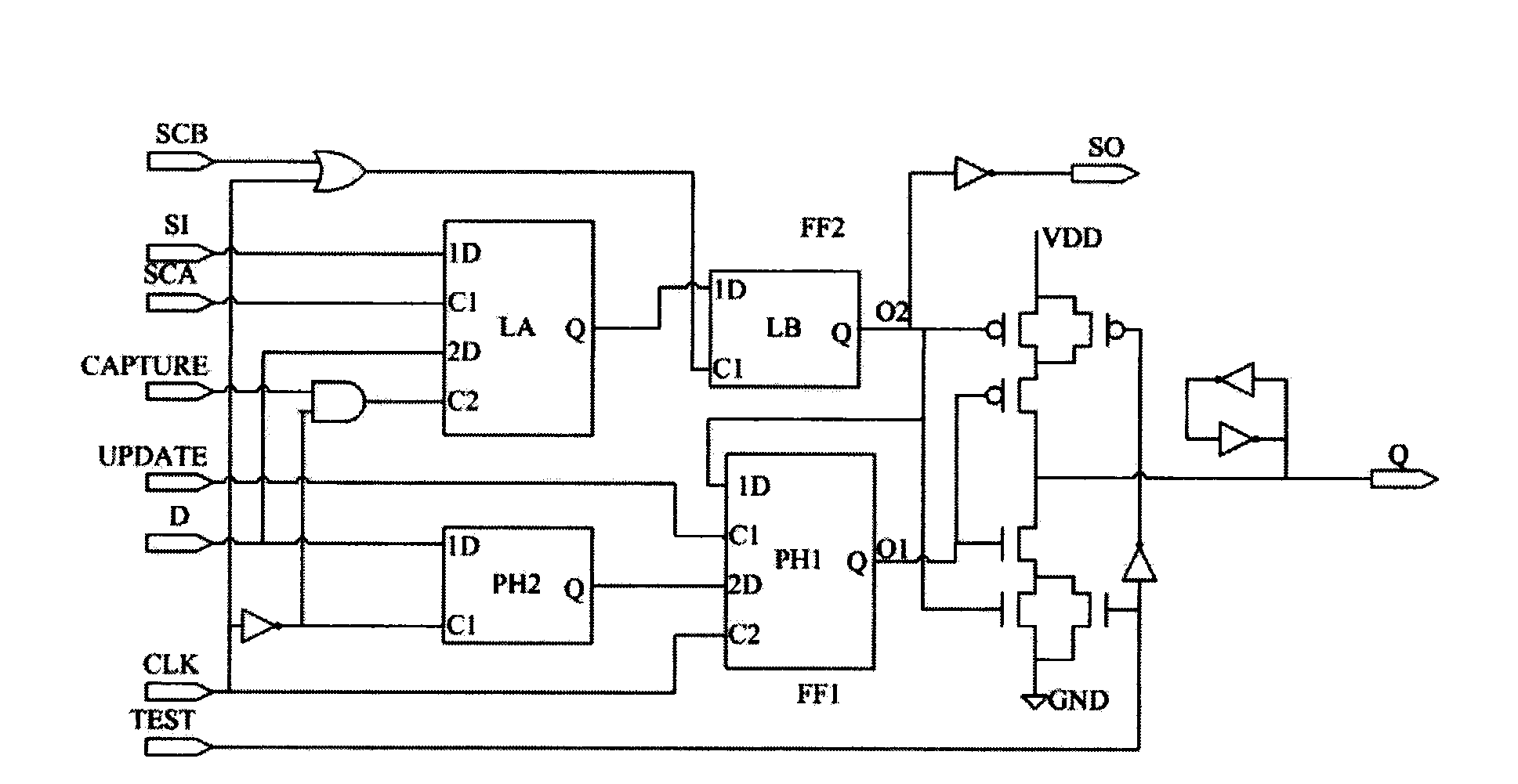

[0041] The present invention provides a scan chain flip-flop that can tolerate soft errors, including a multiplexer (MUX), a parallel flip-flop module (Multi-FF), a soft error processing unit (C-element) and a holding circuit (Keeper) . Its structure diagram is as follows Figure 5 shown.

[0042] The soft-error-tolerant scan chain flip-flop provided by the present invention has three working modes, which are fault-tolerant mode, scan test mode and low power consumption mode.

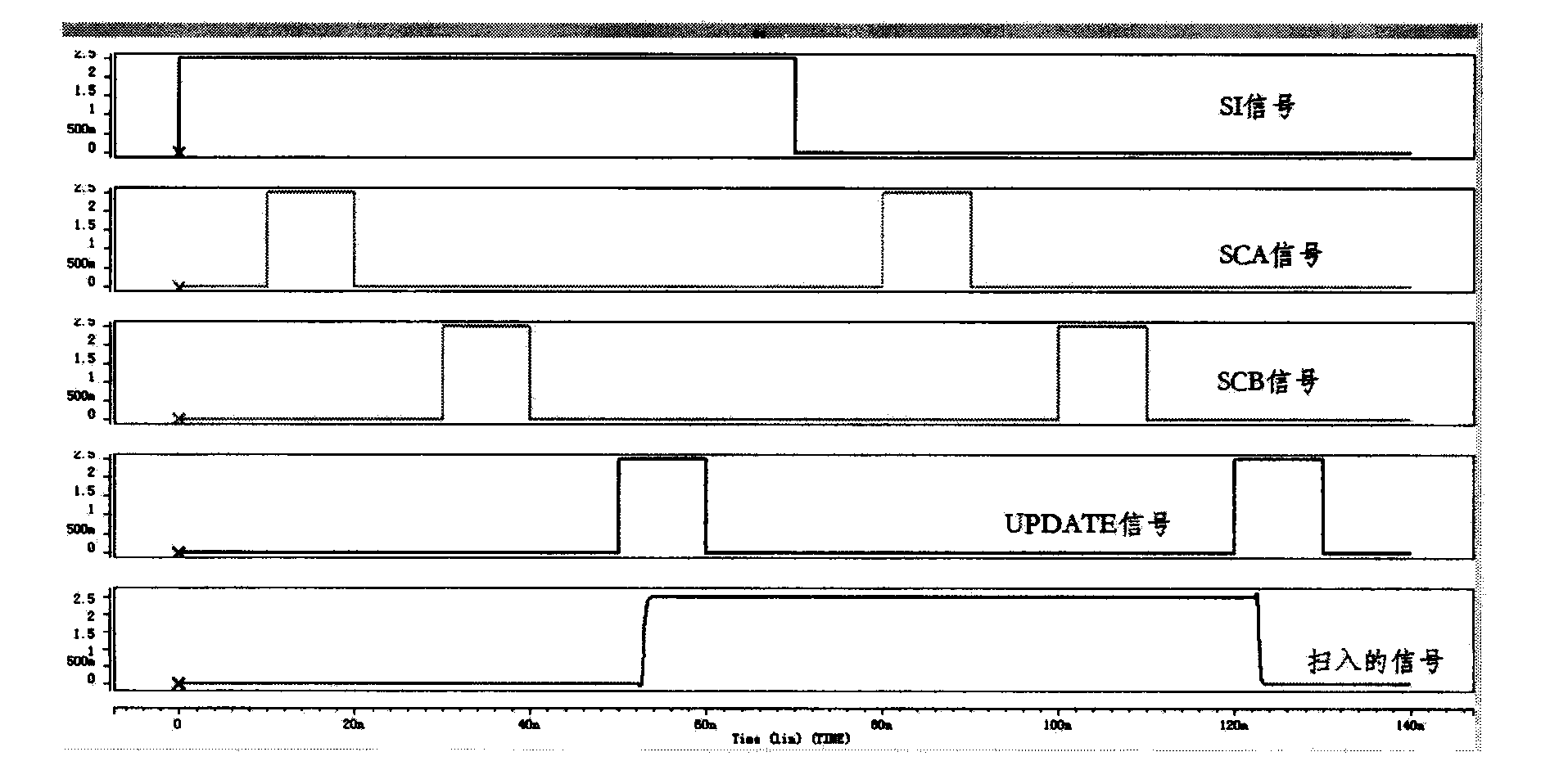

[0043] Due to the existence of the C-element, the soft-error tolerant scan chain flip-flop provided by the present invention needs to be connected to an inverter at the output end when it is actually used. The circuit provided by the present invention is simulated and analyzed by using HSPICE, the simulation experiment is based on TS...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More