Embedded independent dual-port BRAM (block RAM) IP hardcore of FPGA (field programmable gate array)

A dual-port, hard-core technology, applied in the FPGA field, can solve problems such as the asynchronous complexity of internal control signal transmission, and achieve the effects of weakened drive capability, reduced mutual pull current, and improved adaptability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

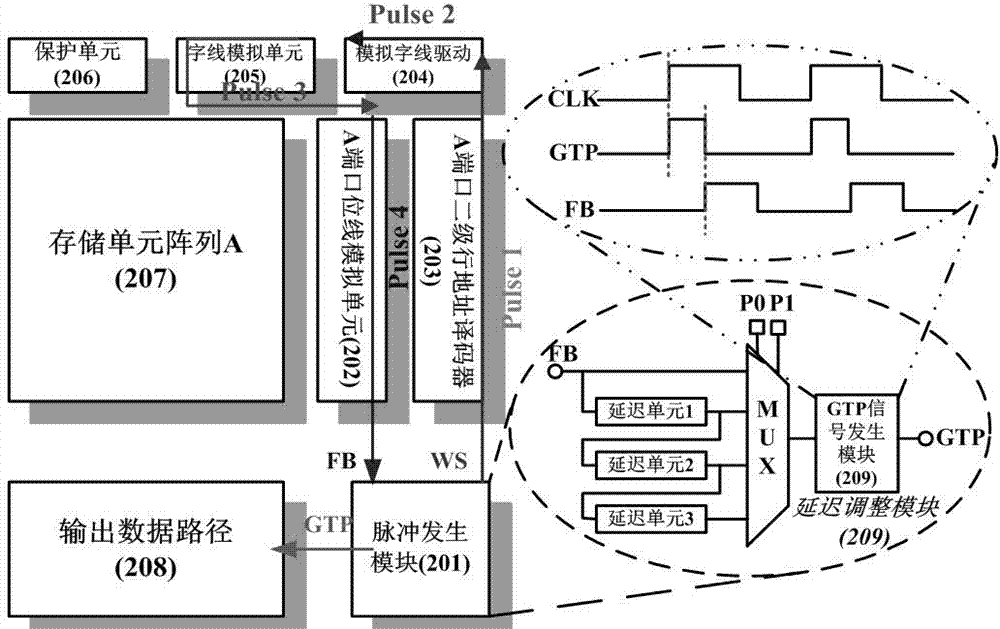

[0031] Such as figure 2 As shown, when the pulse generator in the overall circuit 201 After the WS work enable control signal is generated, the pulse signal Pulse1 will first pass through the word line analog drive unit 204 , the delay of the output pulse Pulse2 compared with the original pulse is that the signal passes through the analog drive unit 204 The delay; then Pulse2 input to the word line analog unit 205 , the delay of the output Pulse3 compared with Pulse2 is the delay corresponding to the signal being transmitted to the corresponding SRAM through the longest word line distance; then Pulse3 is input to the bit line analog drive unit 202 , the delay of the output Pulse4 compared with Pulse3 is the delay corresponding to the transmission of the signal to the corresponding SRAM through the longest bit line distance; finally the Pulse4 pulse is fed back to the pulse generation module 201 , the write / read operation is controlled by the obtained overall delay, because...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More