Universal floating point full-pipeline FFT (Fast Fourier Transform) operation IP (Internet Protocol) core

A pipelined, floating-point technology, applied in computing, instrumentation, electrical and digital data processing, etc., can solve problems such as poor real-time performance, insufficiently optimized FFT processing architecture, and no full pipeline operation.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The technical solutions in the embodiments of the present invention will be clearly and completely described and discussed below in conjunction with the accompanying drawings of the present invention. Obviously, what is described here is only a part of the examples of the present invention, not all examples. Based on the present invention All other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

[0036] In order to facilitate the understanding of the embodiments of the present invention, specific embodiments will be taken as examples for further explanation below in conjunction with the accompanying drawings, and each embodiment does not constitute a limitation to the embodiments of the present invention.

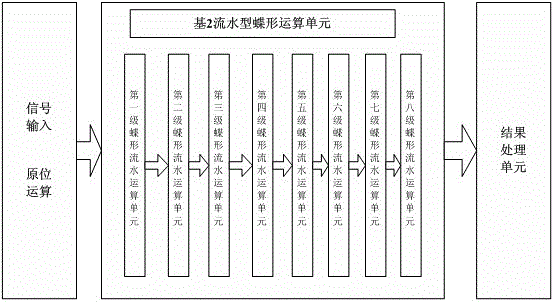

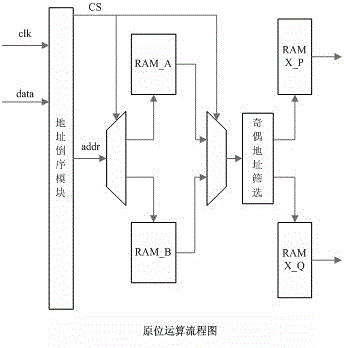

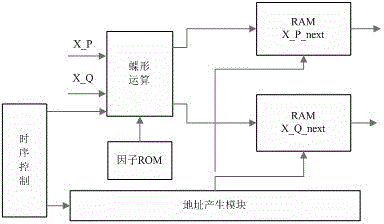

[0037] Please refer to figure 1 , a general-purpose floating-point full-pipelined FFT computing IP core provided in this embodiment includes: an in-situ computing unit, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More