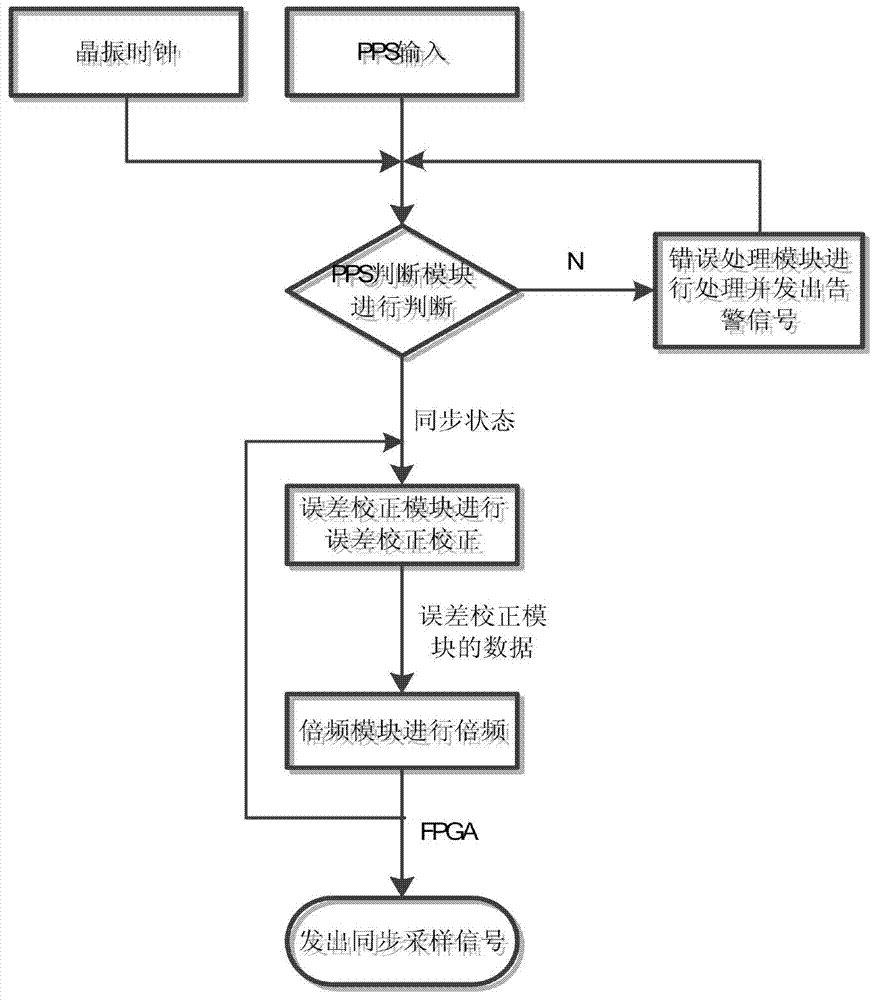

Synchronous sampling clock closed loop correcting method and system based on FPGA

A closed-loop correction and synchronous sampling technology, used in clocks, electronic timers, changing time indications, etc., can solve the problems of large output error and strong dependence on crystal oscillators, and achieve the effect of improving output accuracy, reducing impact and saving production costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0047] Error analysis of synchronous sampling clock:

[0048] In this synchronous sampling clock, due to the rounding operation during Baund_inc calculation, an error will be generated at the nth synchronous resampling signal:

[0049] ξ 2 = | n F res - n · 2 W Baund _ inc · 1 F cry | - - - ( 6 )

[0050] Since the error of the reacquisition signal is corrected once per second during synchronization, when n takes the maximum value of 4000 and the Baund_inc rounding error is at most 1, that is, n=4000, When, ξ 2 has a maximum v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com