Optimizing method for integrated circuit clock grid driving based on driving window

A clock grid, integrated circuit technology, applied in electrical digital data processing, special data processing applications, instruments, etc., can solve the problems of difficult timing convergence, poor layout, wiring congestion, etc., to achieve good scalability and save chips The effect of area occupancy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

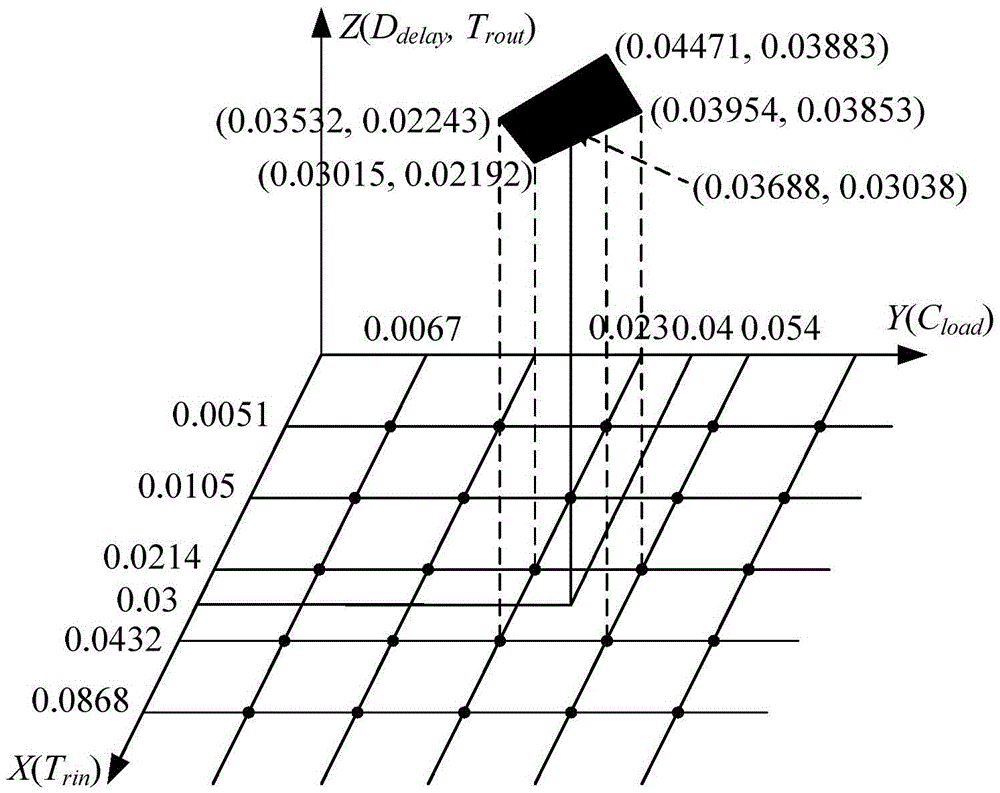

[0023] Such as Figure 4 As shown, the implementation steps of the integrated circuit clock grid driving optimization method based on the driving window in this embodiment are as follows:

[0024] 1) Based on the low-pass filtering characteristics, the clock grid of the integrated circuit is divided into multiple driver windows according to the influence range of each driver, and one driver window is taken as the current driver window, and then jump to step 2).

[0025] In this embodiment, the driving window obtained by separating the clock grid of the integrated circuit is a rectangular window, and each main intersection point of the clock grid is located at the center of the rectangular window, specifically as follows Figure 5 As shown in , the triangles in the figure represent the drivers placed at the intersections of the backbones of the grid, and each rectangular area represents the influence range of the corresponding driver—the driving window, and the small black dots...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More