Autonomous configuration method for FPGA (field programmable gate array)-based embedded dual-core system

A configuration method and embedded technology, applied in the direction of program control device, program loading/starting, etc., can solve problems such as inability to store and load configuration files

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

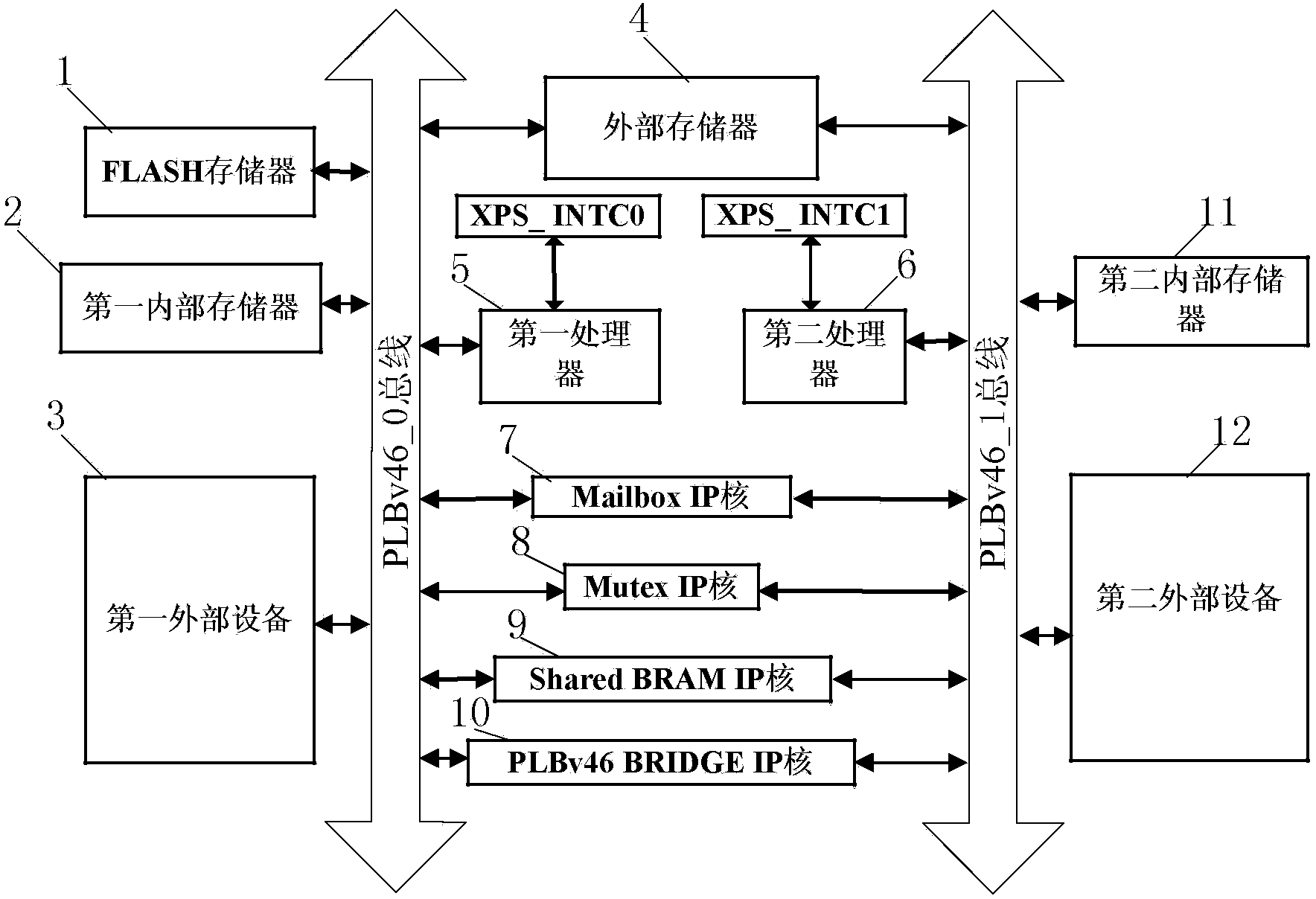

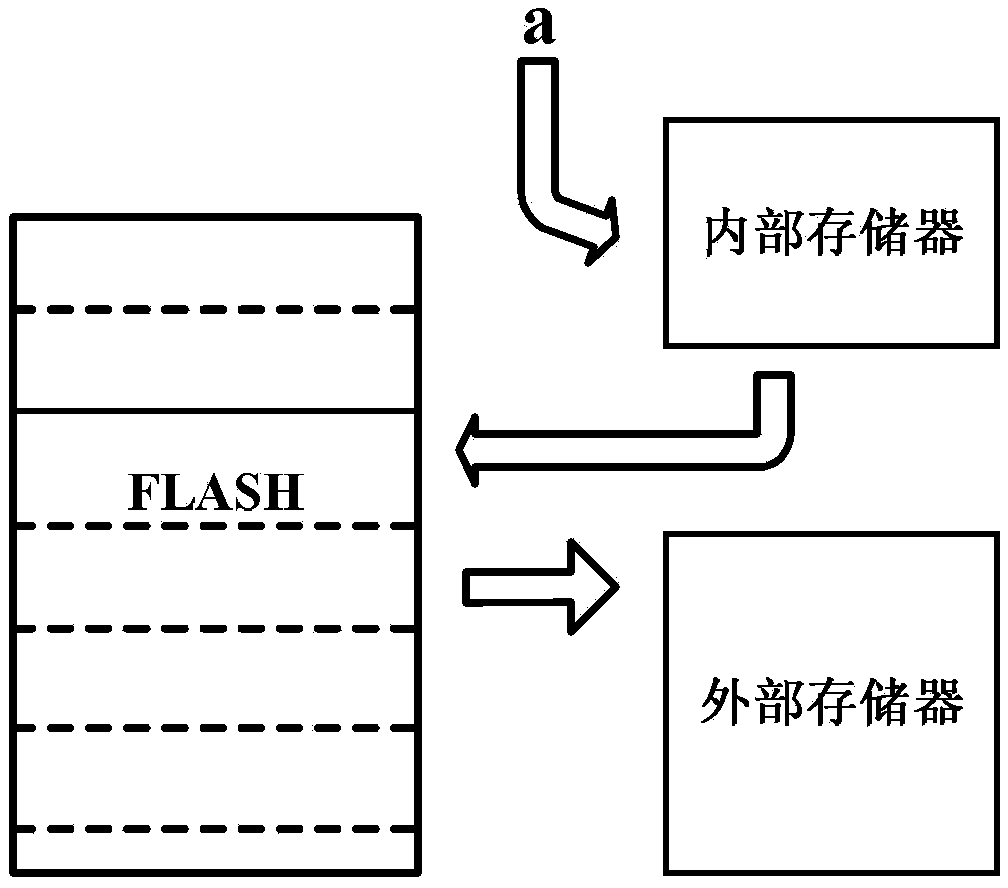

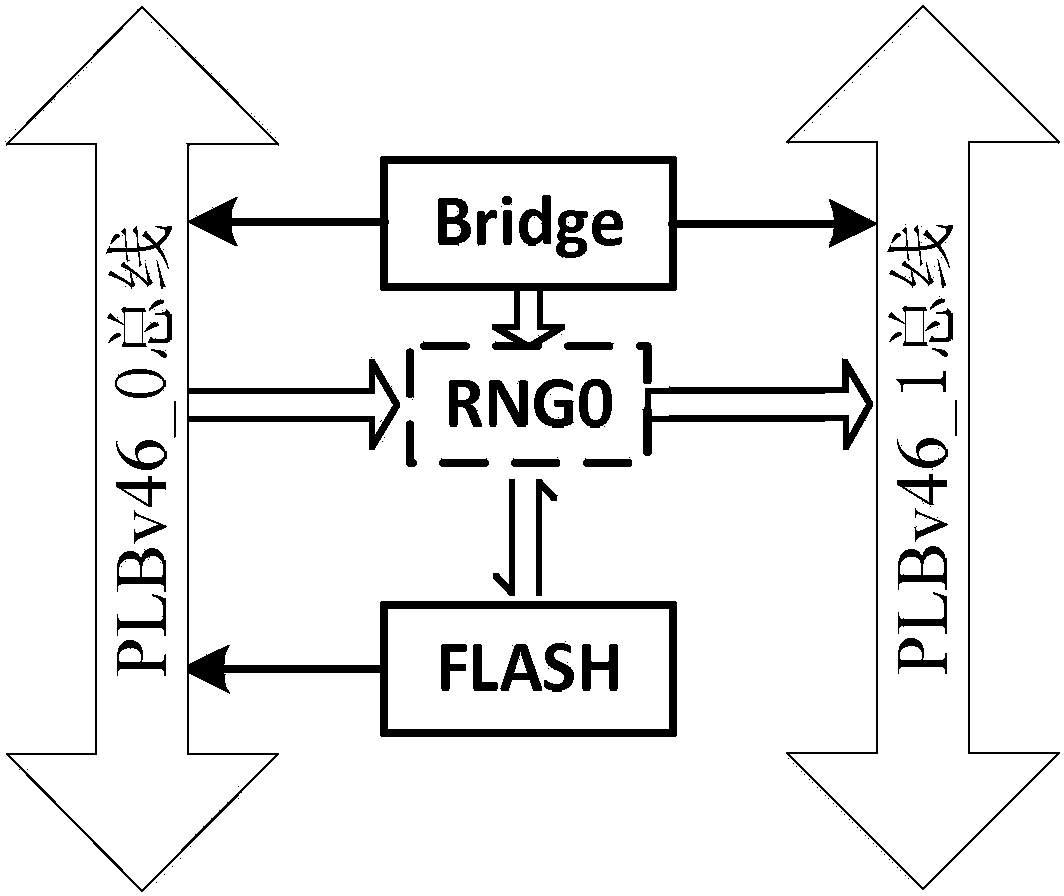

[0018] Specific implementation mode 1. Combination figure 1 with Figure 4 Illustrate this embodiment, the autonomous configuration method of the FPGA-based embedded dual-core system described in this embodiment, the FPGA-based embedded dual-core system includes a FLASH memory 1, a first internal memory 2, a first external device 3, an external Memory 4, first processor 5, second processor 6, MailboxIP core 7, Mutex IP core 8, Shared BRAM IP core 9, PLBv46BRIDGE IP core 10, second internal memory 11 and second external device 12,

[0019] The FLASH memory 1, the first internal memory 2 and the first external device 3 and the external memory 4, the first processor 5, the Mailbox IP core 7, the Mutex IP core 8, the Shared BRAM IP core 9 and the PLBv46BRIDGE IP core 10 pass through the PLBv46_0 bus for data exchange,

[0020] The external memory 4, the second processor 6, the Mailbox IP core 7, the Mutex IP core 8, the Shared BRAM IP core 9 and the PLBv46BRIDGE IP core 10 excha...

specific Embodiment approach 2

[0030] Embodiment 2. The difference between this embodiment and the autonomous configuration method of the FPGA-based embedded dual-core system described in Embodiment 1 is that the FLASH memory 1 is implemented with a model of JS28F256P30.

specific Embodiment approach 3

[0031] Embodiment 3. The difference between this embodiment and the autonomous configuration method of the FPGA-based embedded dual-core system described in Embodiment 1 is that the external memory 4 is realized by a DDR2 memory model WD2RE01GX809-667G-PE.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More