Fin type field effect transistor forming method

A fin field effect transistor and fin technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of fin field effect transistor threshold voltage offset, fin 11 damage, error, etc., Achieve the effect of avoiding threshold voltage shift, improving stability and good uniformity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

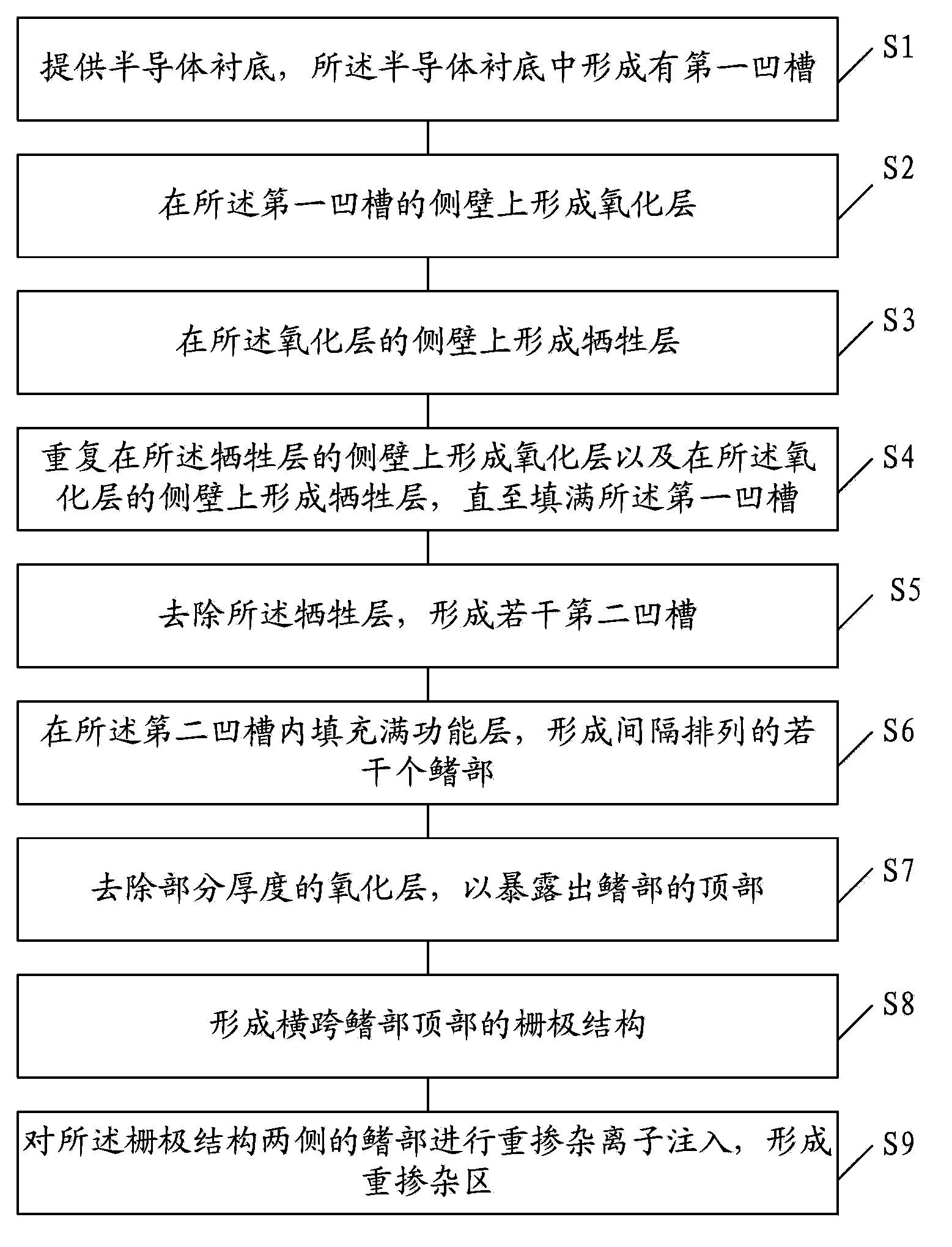

[0019] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0020] In the following description, many specific details are set forth in order to fully understand the present invention, but the present invention can also be implemented in other ways than those described here, so the present invention is not limited by the specific embodiments disclosed below.

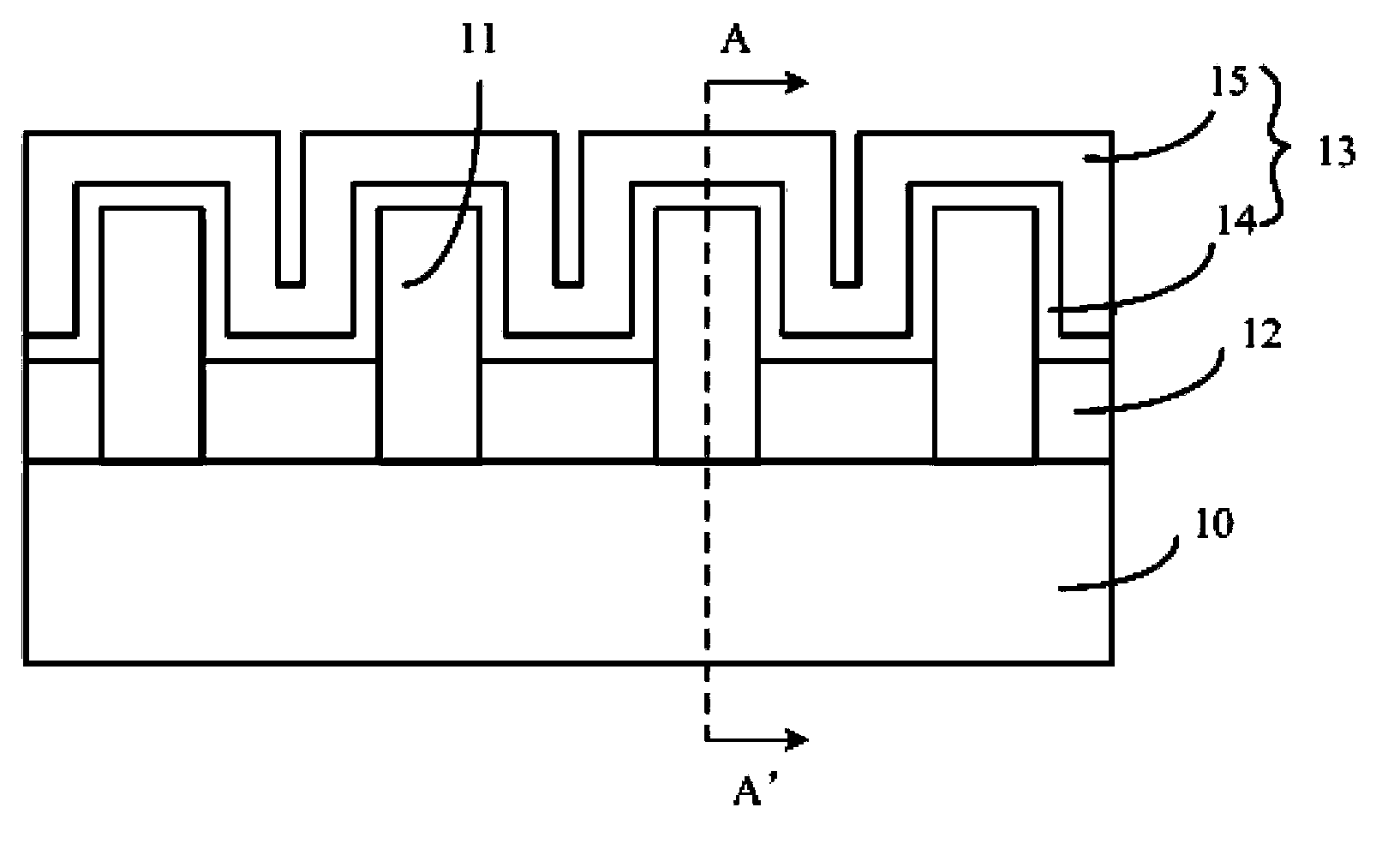

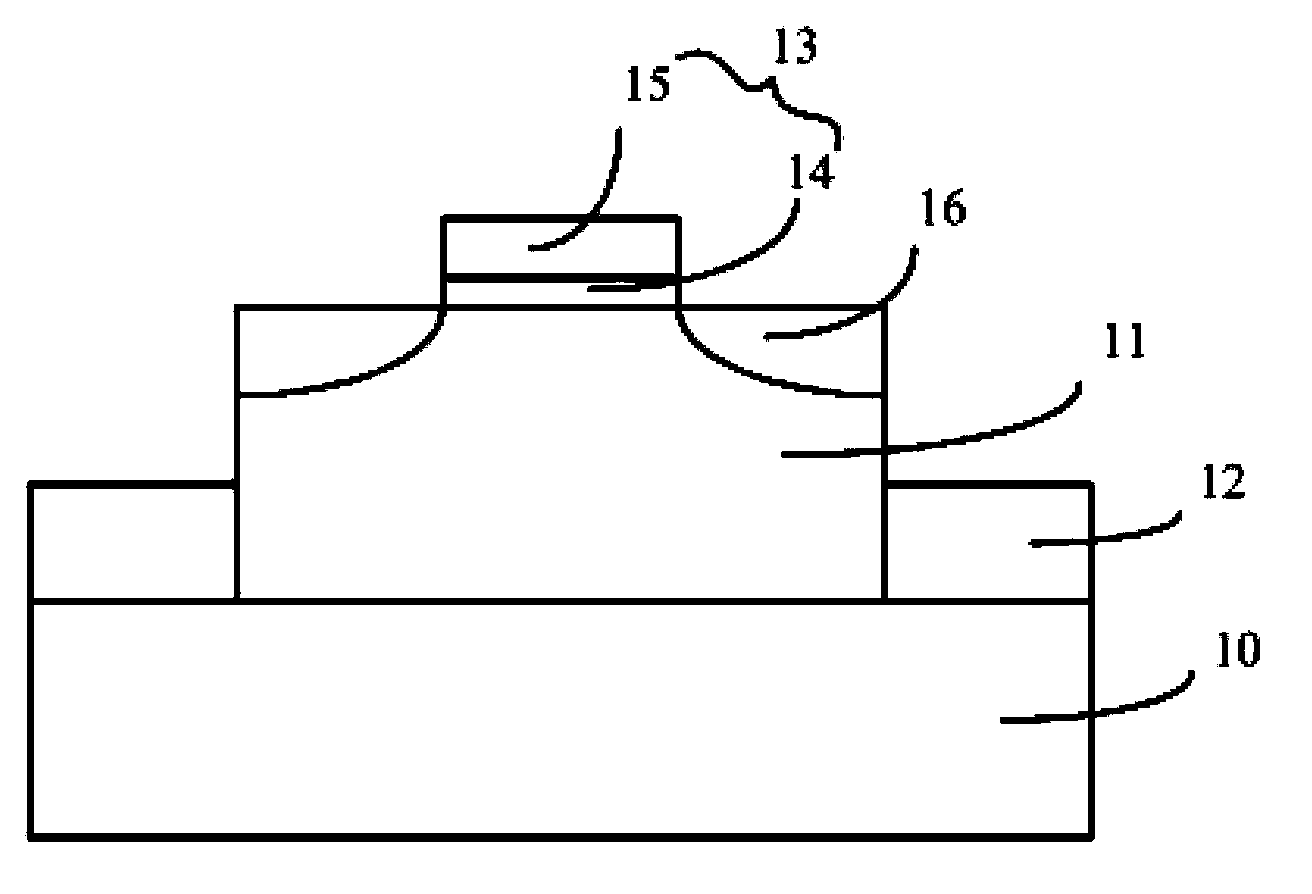

[0021] As mentioned in the background technology section, in the prior art, when the fins of the fin field effect transistors are formed by dry etching the semiconductor substrate, the thickness of the formed fins cannot be precisely controlled, and the formed fin field effect transistors are The difference in electrical performance due to different channel widths; moreover, the dry etching process will cause damage to the surface of the f...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Height | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More