Method For Fabricating Semiconductor Package

A semiconductor and packaging technology, applied in the field of semiconductor packaging manufacturing methods, can solve the problems of semiconductor chip offset, manufacturing cost cannot be reduced, redistribution circuit layer offset chip electrical connection, etc., to improve product yield. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

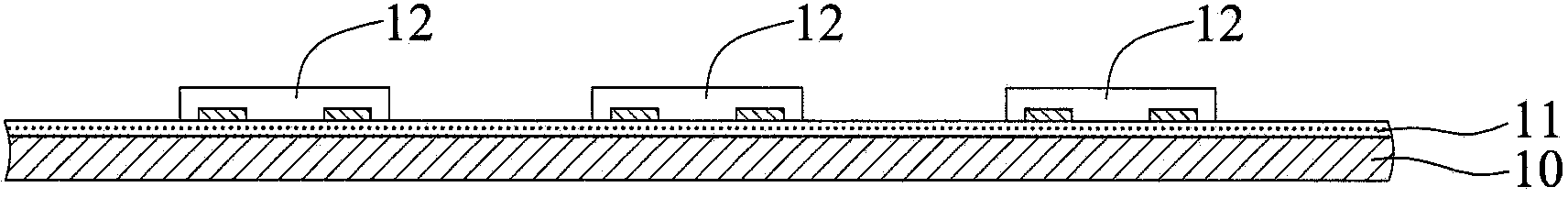

[0053] The following will match Figure 2A to Figure 2H A schematic cross-sectional view of the first embodiment of the manufacturing method of the semiconductor package of the present invention is described in detail.

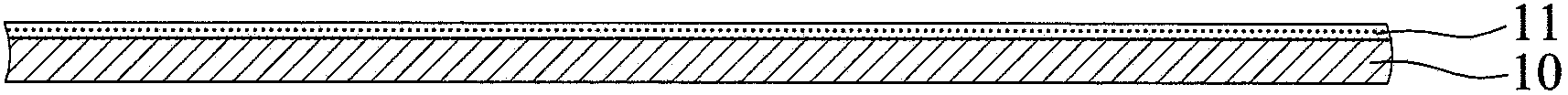

[0054] Such as Figure 2A As shown, a carrier plate 20 is provided, and a release layer 21 is formed on the carrier plate 20, and the material of the carrier plate 20 is glass, and the material of the release layer 21 is amorphous silicon (Amorphous Silicon), Parylene or amorphous phase-silicon dioxide (α-SiO 2 ), the release layer 21 can be formed by chemical vapor deposition (Chemical Vapor Deposition, CVD).

[0055] Such as Figure 2B As shown, a metal layer 22 is formed on the release layer 21, and is formed by, for example, plasma-assisted chemical vapor deposition (Plasma Enhance Chemical Vapor Deposition, PECVD), chemical vapor deposition (Chemical Vapor Deposition, CVD), physical vapor deposition (Physical The metal layer 22 is formed by Vapor Depo...

no. 2 example

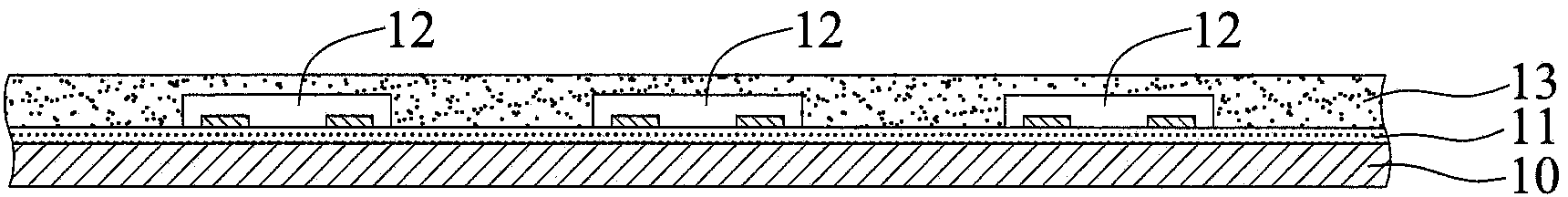

[0064] see image 3 , which is a schematic cross-sectional view of the second embodiment of the manufacturing method of the semiconductor package of the present invention.

[0065] This embodiment is substantially the same as the previous embodiment, the main difference is that this embodiment does not use the metal layer 22, but the adhesive layer 23' used is distributed with a plurality of metal particles, and the metal particles are used to block the The light a passes through the adhesive layer 23 ′, and other steps in this embodiment are similar to those in the previous embodiment, so details are not repeated here.

no. 3 example

[0067] see Figure 4 , which is a schematic cross-sectional view of the third embodiment of the manufacturing method of the semiconductor package of the present invention.

[0068] This embodiment is substantially the same as the second embodiment, and the main difference is that the metal particles 30 of this embodiment are composed of silicon oxide spheres 30a and a metal coating layer 30b formed on the surface of the silicon oxide spheres 30a. The metal particles 30 can block the light a from passing through the adhesive layer 23 ′, and other steps of this embodiment are similar to those of the second embodiment, so details are not repeated here.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More