Standard cell design method resistant to single-particle latch-up effect

A standard cell and latch-up effect technology, applied in computing, special data processing applications, instruments, etc., can solve problems such as limiting the working speed and scale of radiation-resistant devices, increasing cell area, parasitic capacitance, and reducing circuit speed, etc., to achieve small Effects of layout design modification, increased flexibility, and mitigation effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

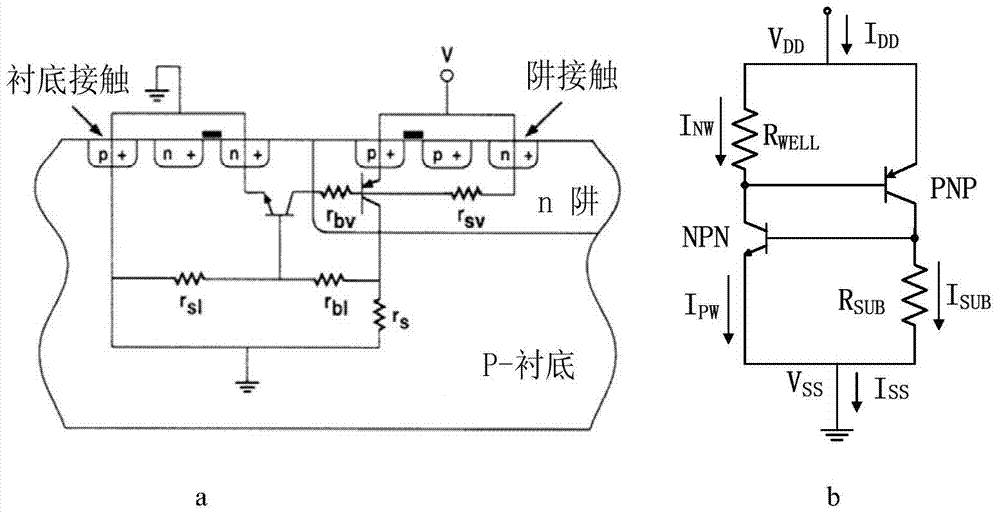

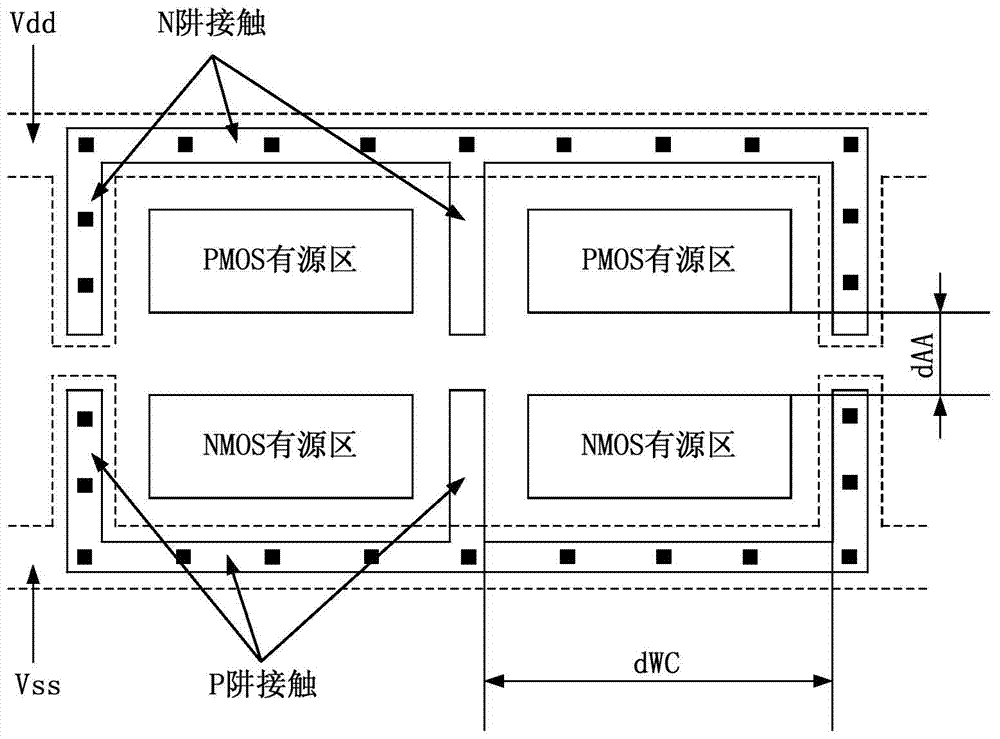

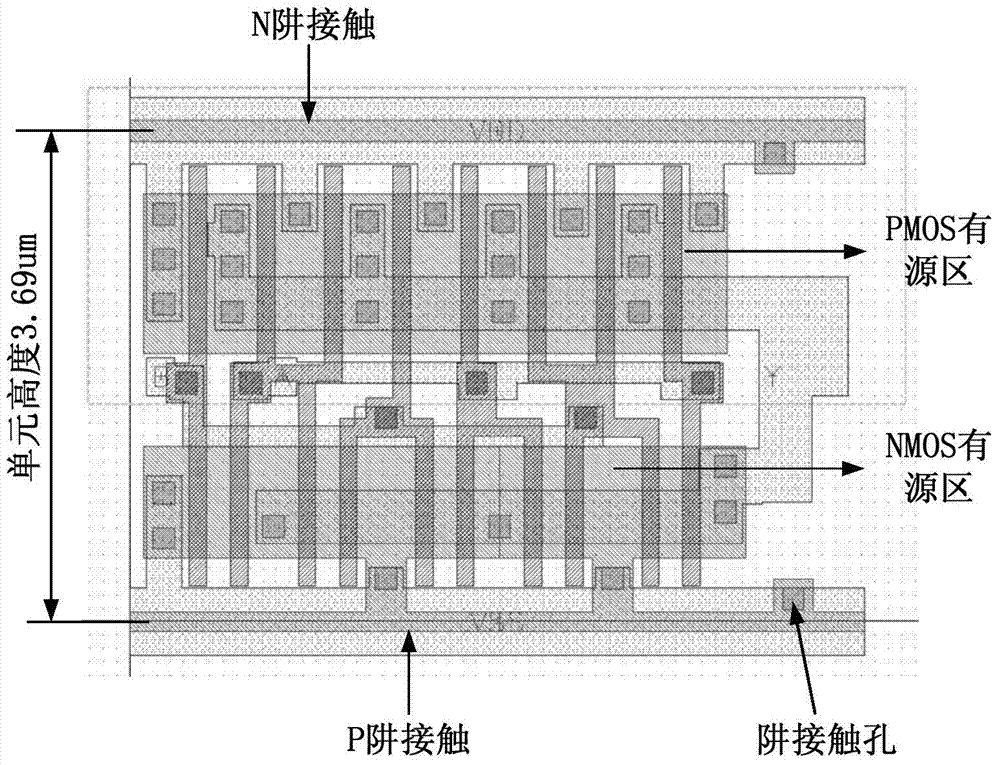

[0025] Combined with the mechanism analysis of single event latch-up effect, the basic principle to avoid latch-up effect is:

[0026] (1) Reduce well / substrate parasitic resistance. When a single event current (IWELL) occurs in the well / substrate p-n junction, reducing the well resistance (RWELL) is equivalent to reducing the voltage drop between the emitter and base of the vertical parasitic PNP transistor in the well, thereby reducing the trigger Risk of parasitic PNP transistor turning on;

[0027] (2) Destroy the characteristics of the parasitic bipolar transistor and reduce the current gain of the transistor. Reducing the gain of the parasitic transistor in the latch structure is equivalent to reducing the feedback loop current gain of the two parasitic transistors, so as to avoid continuous increase of the positive feedback loop current in the latch structure.

[0028] Aiming at the damage mechanism of spatial single event latch-up effect to CMOS integrated circuits, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More