Method for Improving Device Negative Bias Temperature Instability

A negative bias temperature and instability technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the effects of negative bias temperature instability, threshold voltage drift, weak gate control capabilities, etc. The problem is to improve the temperature instability of negative bias voltage, reduce the drift of threshold voltage, and reduce the generation of H+

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

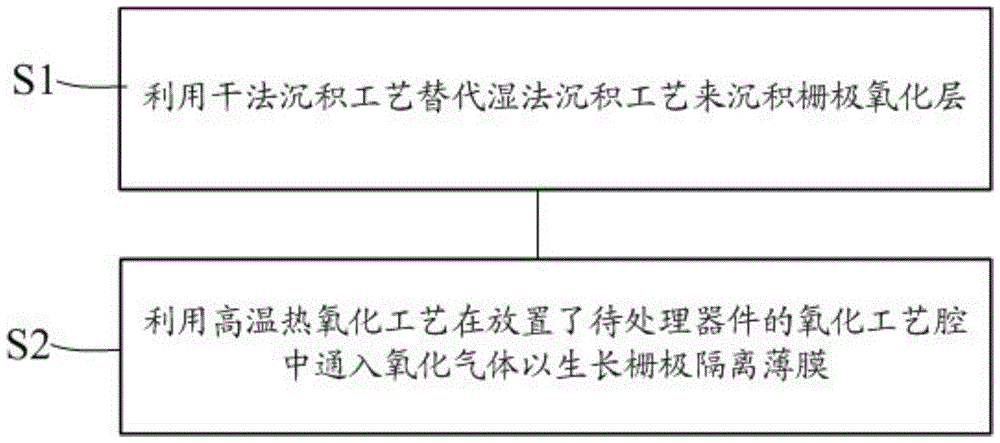

[0015] In the reliability analysis of semiconductor devices, the negative bias temperature instability NBTI (Negative bias temperature instability) is a very important consideration parameter, aiming at improving the negative bias temperature instability NBTI of the device, the present invention adds In the deposition process, dry oxidation is used instead of wet deposition, and chlorine-doped HTO (thermal oxidation) is used for the growth of gate spacers, thereby reducing the generation of H+ and reducing the number of trapped charges in the positive oxide layer , improving the negative bias temperature instability NBTI of the device.

[0016] Specifically, by changing the wet deposition of the gate oxide layer deposition process in the existin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More