A method of speeding up dram sense amplifiers

A sensitive amplifier and voltage technology, applied in the field of memory, can solve problems affecting the reliability of DRAM memory cells

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

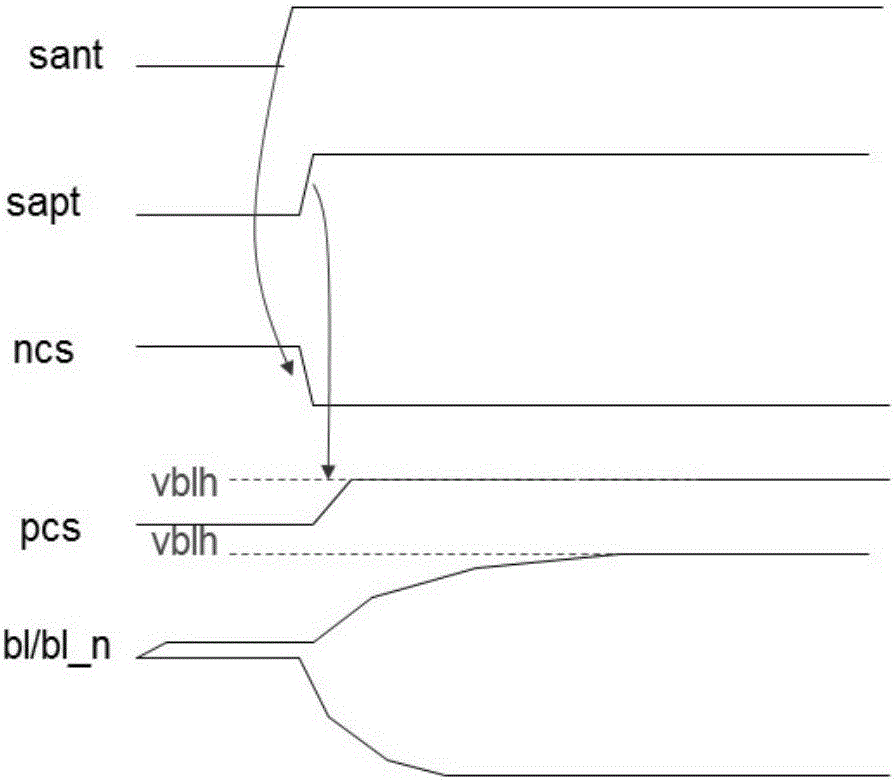

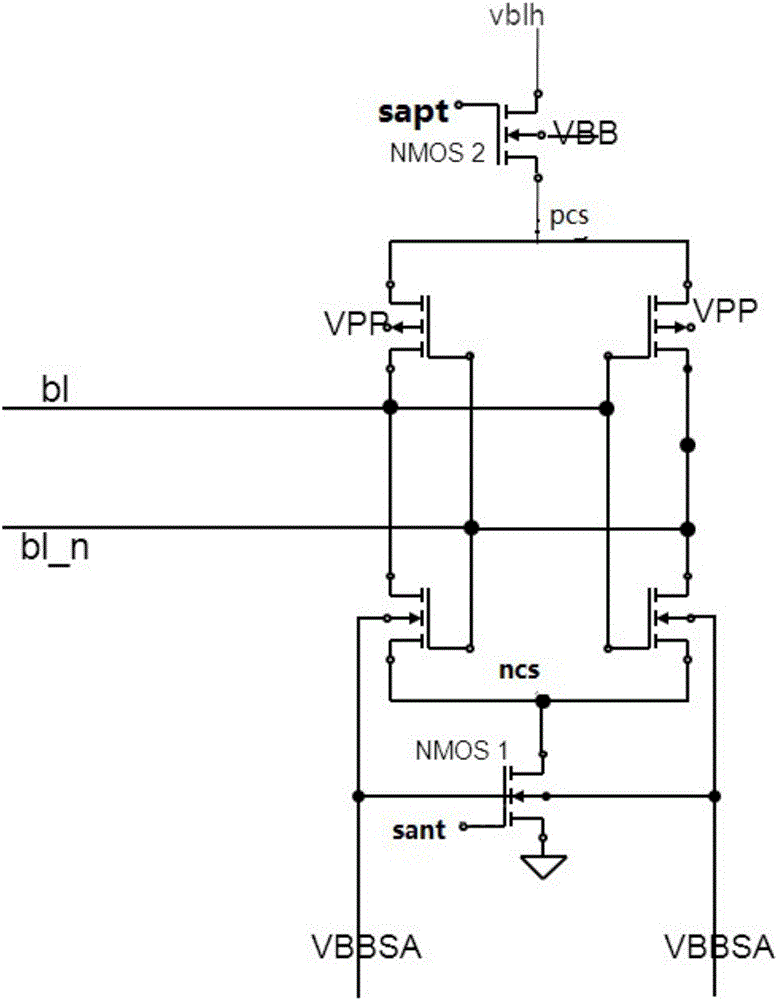

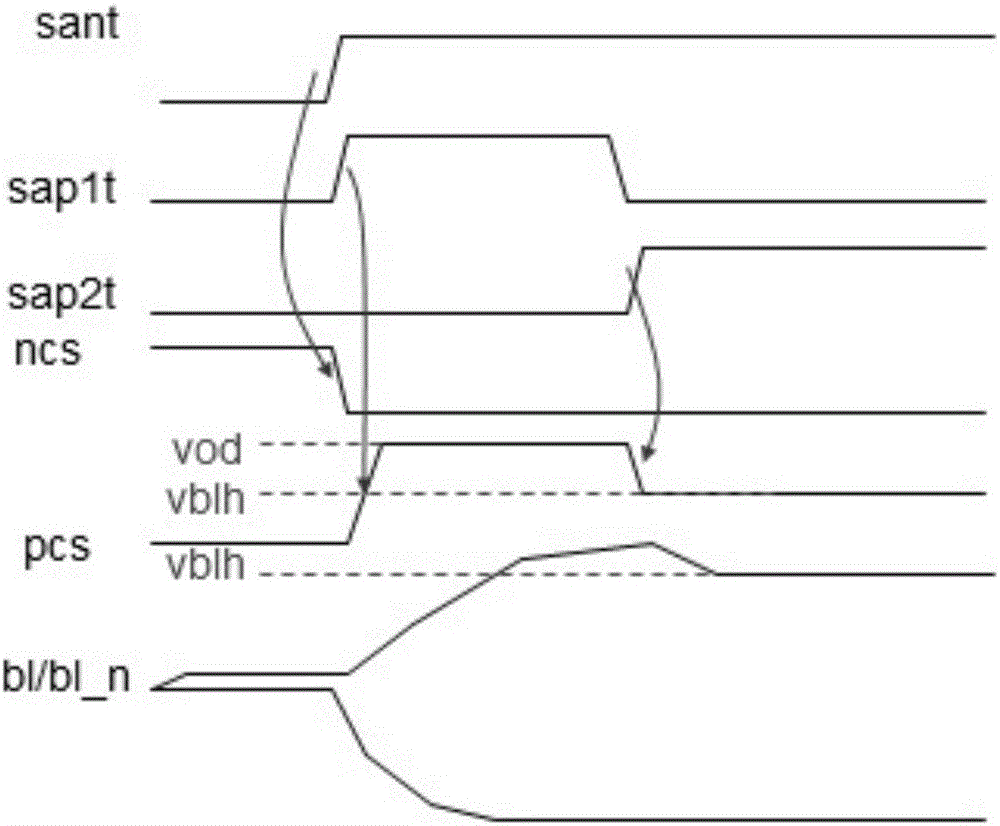

[0025] see image 3 and Figure 4 As shown, in order to improve tRCD (that is, to speed up the amplification speed of the sense amplifier), a method for accelerating the DRAM sense amplifier of the present invention includes the following steps:

[0026] The gate signal sant of NMOS1 is raised to turn on NMOS1, so that the drain signal ncs of NMOS1 is pulled down to the ground voltage, and the reference bit line bl_n starts to be pulled to the ground voltage;

[0027] Then, the gate signal sap1t of NMOS3 is raised to a high level, making NMOS3 turn on, the source signal pcs of NMOS3 is pulled up to vod, the voltage of the bit line bl is quickly pulled up to higher than the voltage vblh, and then the gate signal of NMOS3 sap1t becomes a low level; the gate signal sap2t of NMOS2 becomes a high level, making NMOS2 conductive, the source signal pcs of NMOS2 is pulled to the voltage vblh, and the bit line bl is slowly reduced to the vblh voltage.

[0028] This method improves the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More