Embedded reconfigurable system based on large-scale coarseness and processing method thereof

A reconstruction system and embedded technology, applied in the direction of electrical digital data processing, special data processing applications, instruments, etc., can solve the problem of low utilization rate of array, long period of high-order FIR filter operation of FIR filter, and low efficiency of FIR operation and other issues to achieve the effect of high flexibility and high efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

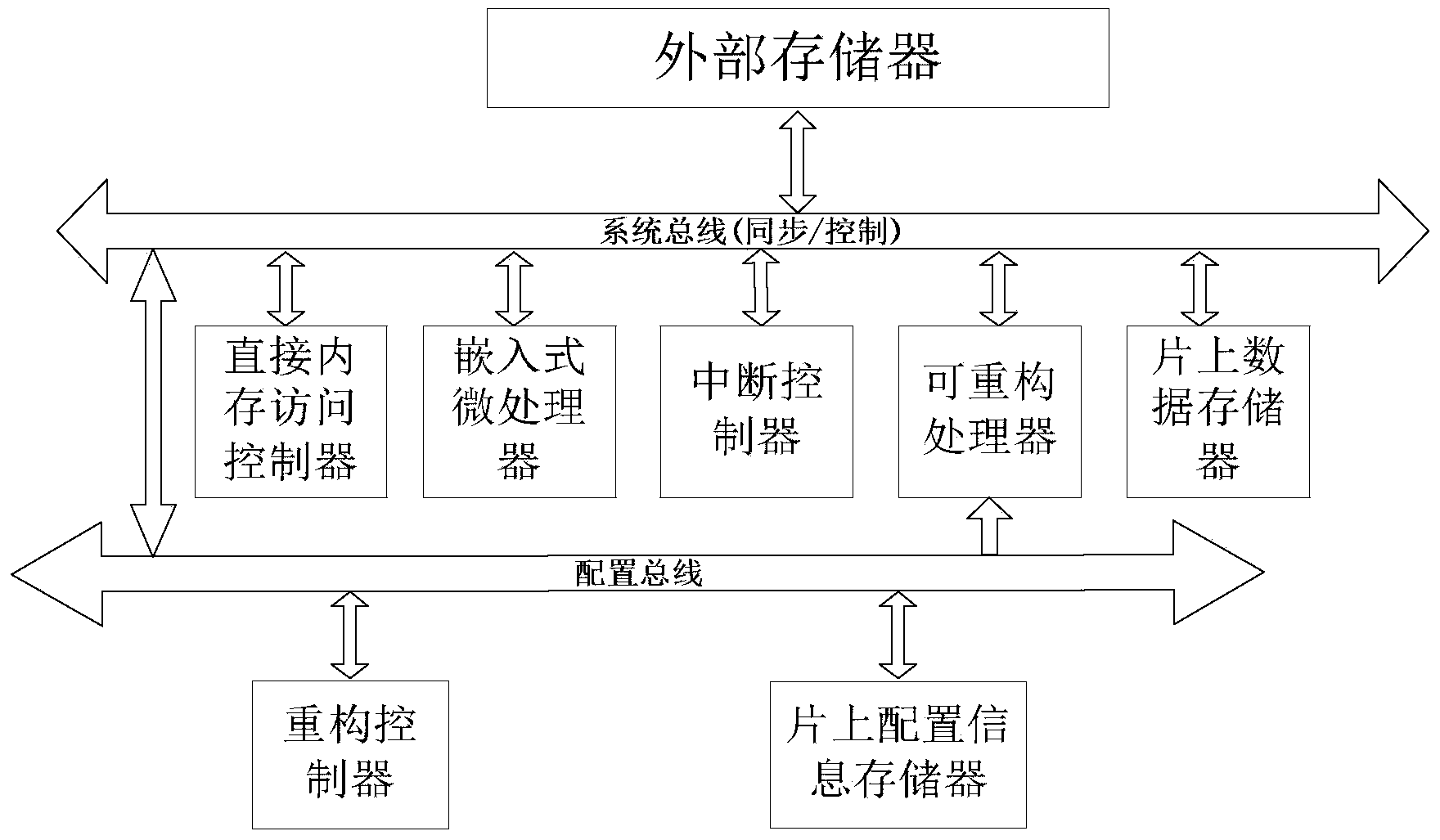

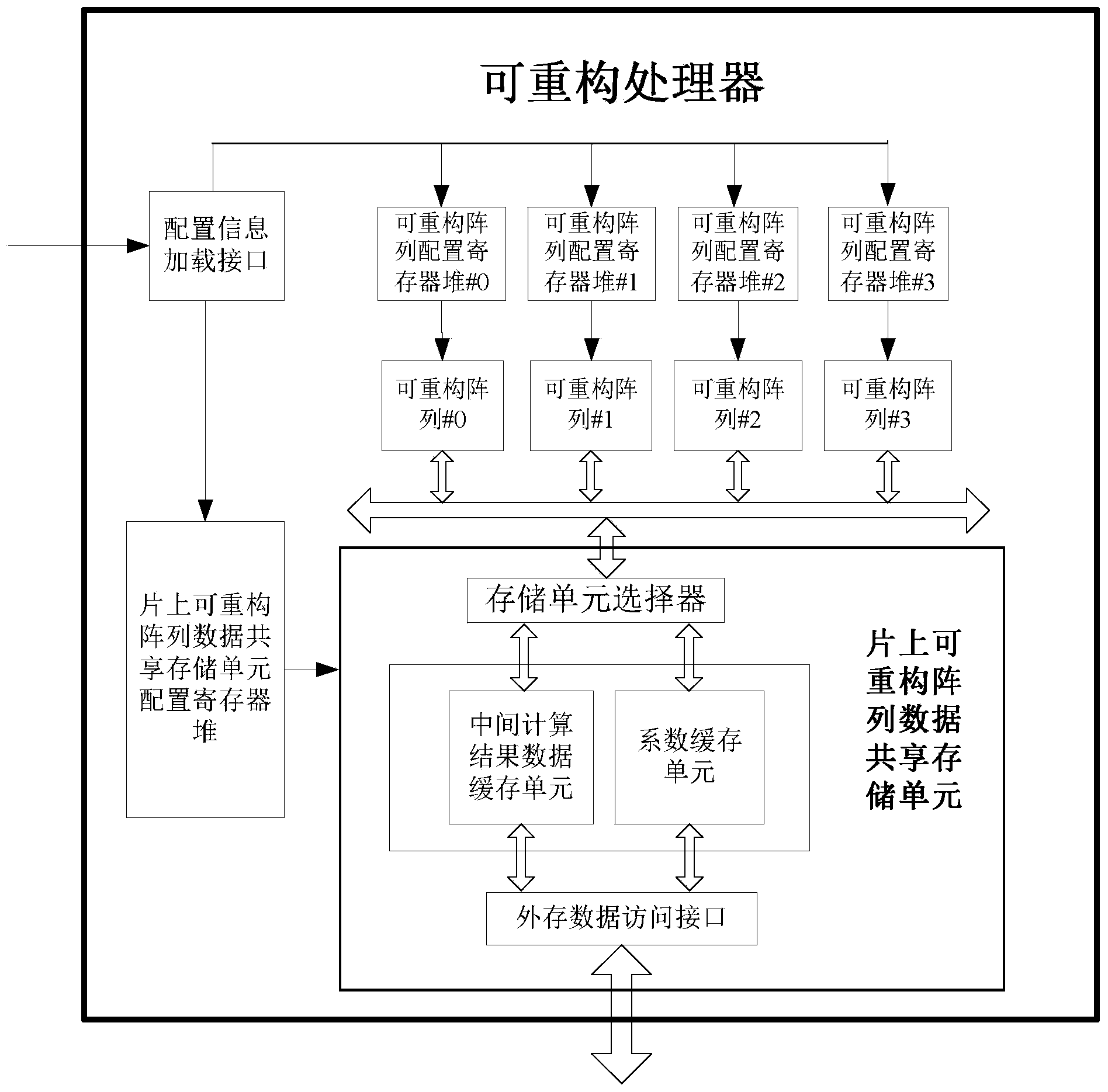

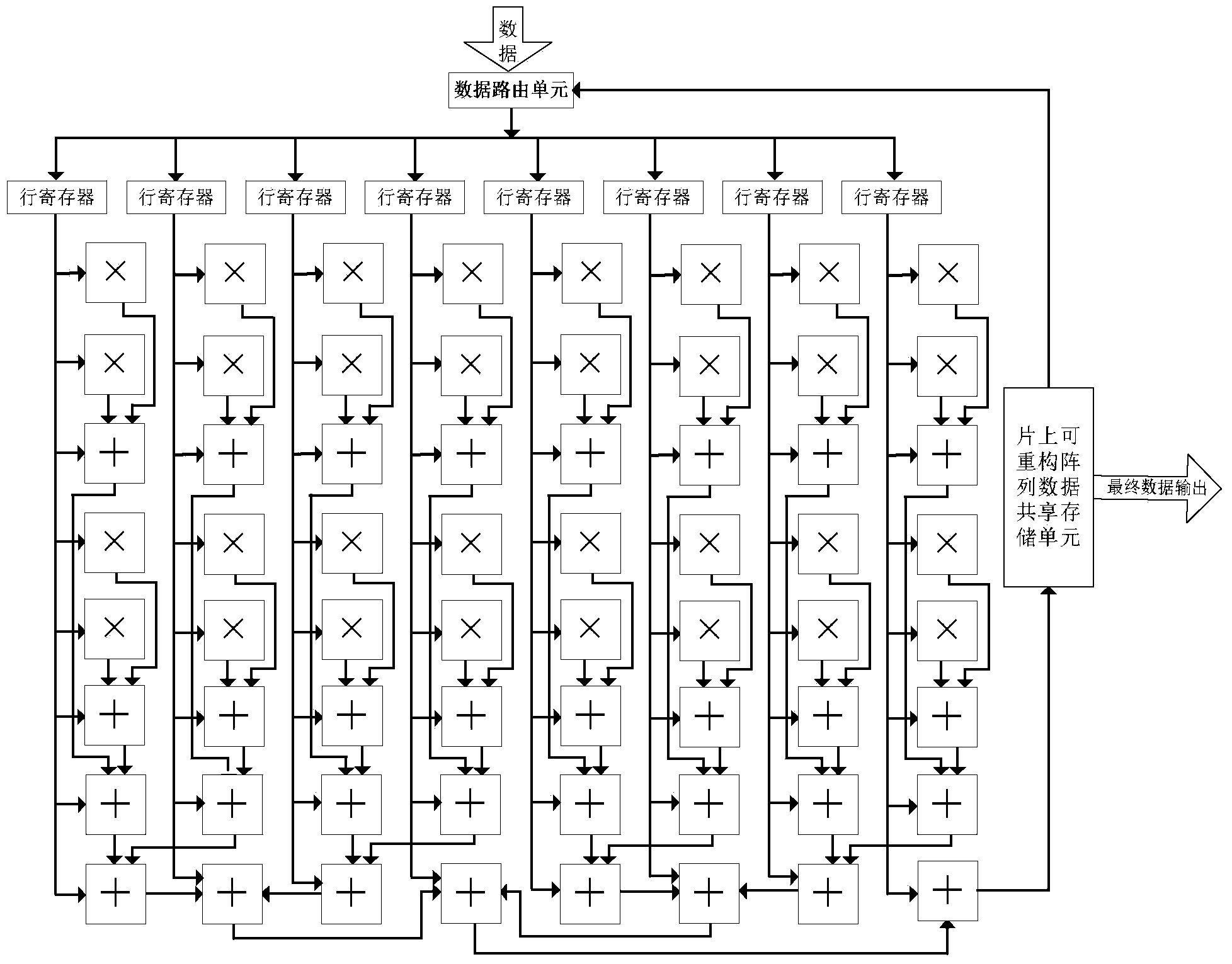

[0038] The present invention will be further described below in conjunction with the accompanying drawings.

[0039] Definition of terms: finite length unit impulse response filter (FIR, Finite Impulse Response), reconfigurable array (RCA, Reconfigurable Array,), ARM920T (a microprocessor name), 32bit AMBA2.0AHB (an embedded High-performance bus name), direct memory access controller (DMAC), computing unit (PE), master device (master), slave device (slaver), embedded reconfigurable array system on chip (system on chip, SoC), interrupt Controller (INTC).

[0040] Table 1 is a description of the reconfigurable array internal registers involved in the implementation method of a finite-length unit impulse response (FIR) filter based on a large-scale coarse-grained dynamic reconfigurable processor of the present invention;

[0041] Table 2 is a description of reconfigurable array configuration information involved in an implementation method of a finite-length unit impulse respons...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More