Logic analyzer with serial bus protocol continuous triggering function

A technology of logic analyzer and serial bus, which is applied in the field of logic analyzer and can solve problems such as failure to provide

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

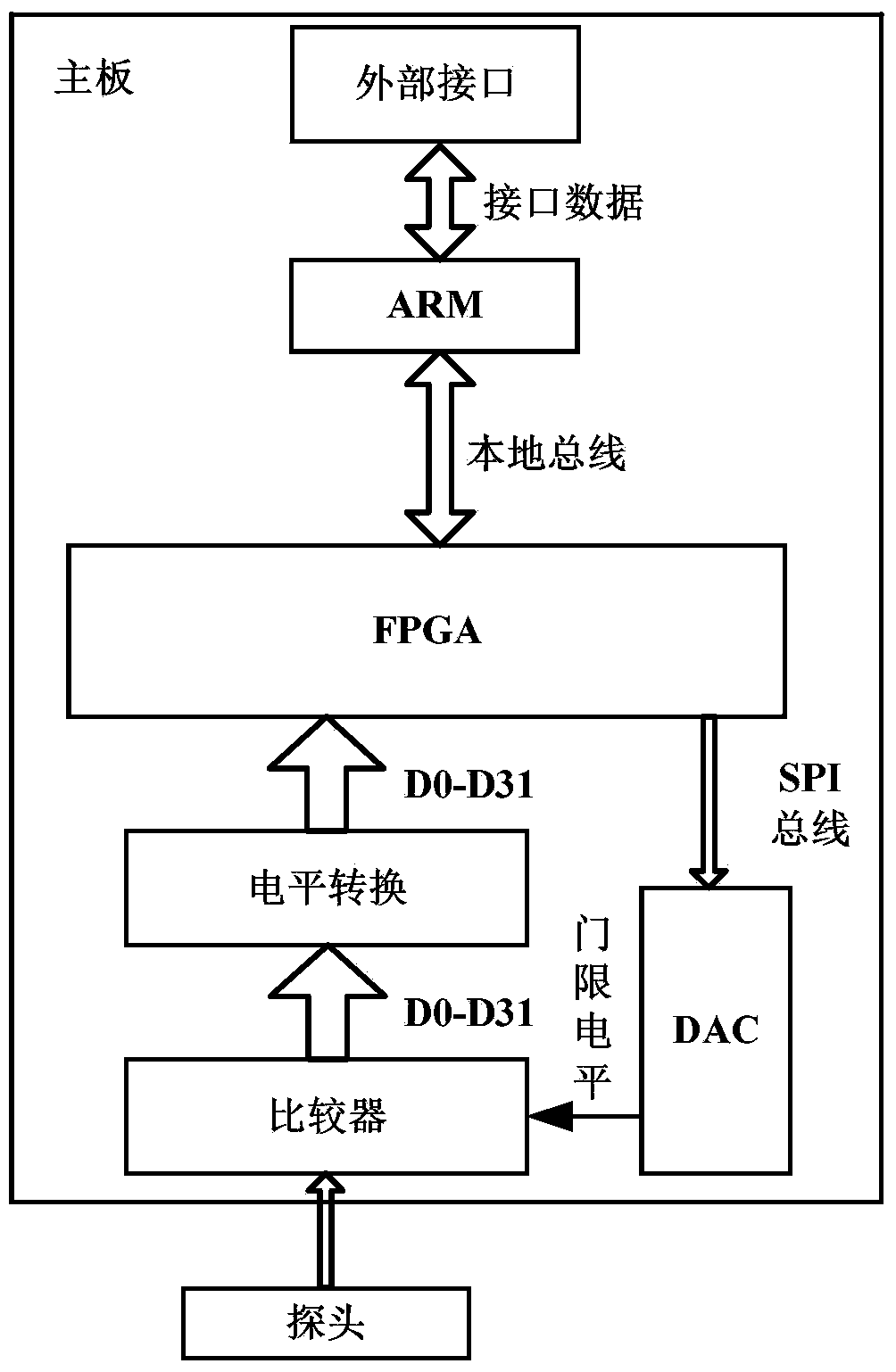

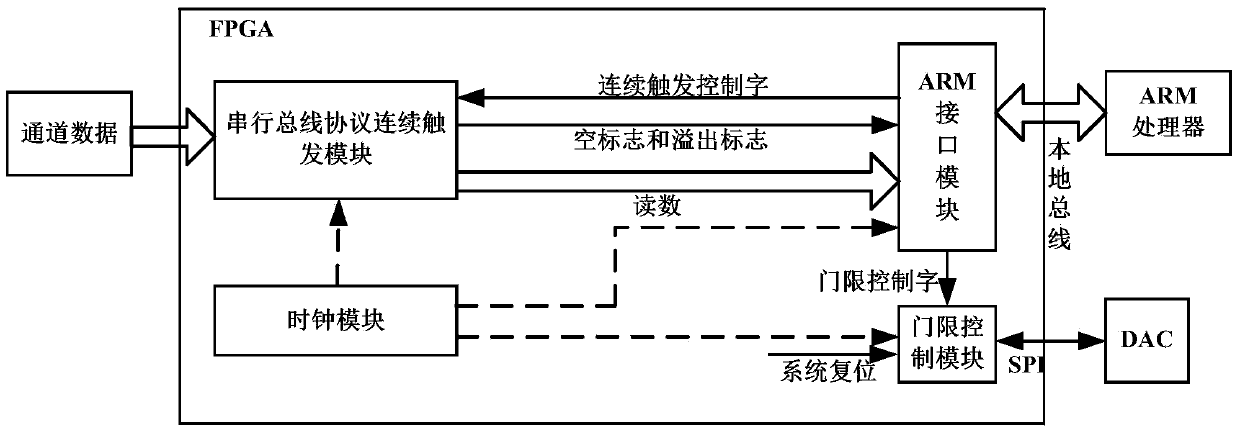

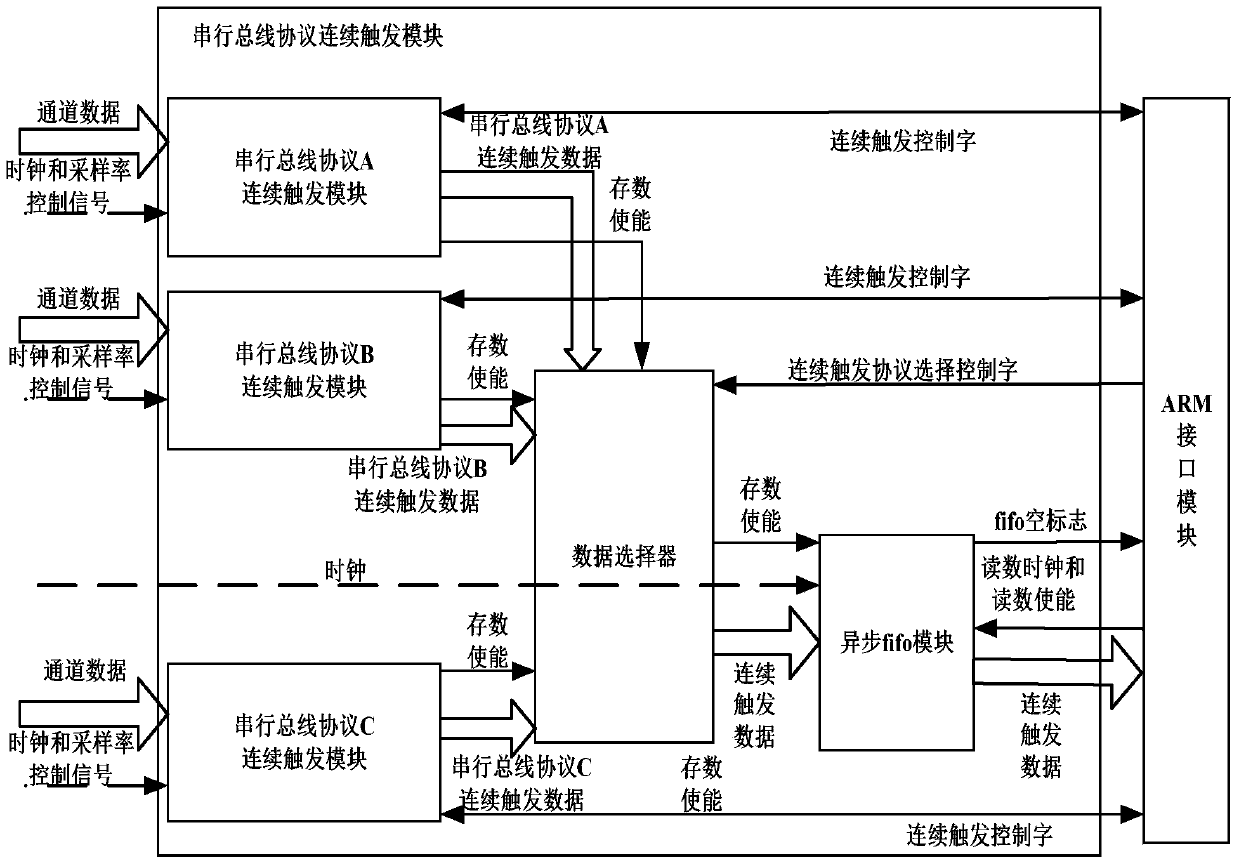

[0025] In order to better illustrate the content of the present invention, a brief introduction to the logic analyzer is firstly made. figure 1 It is a schematic diagram of a logic analyzer in the present invention. Such as figure 1 As shown, like common logic analysis, the channel part of the logic analyzer of the present invention adopts probe+comparator+level conversion+DAC (Digital to Analog Converter, digital-to-analog converter), and DAC is subjected to FPGA (Field-Programmable Gate Array , Field Programmable Gate Array) control the output threshold threshold level to the comparator; the comparator completes the analog-to-digital conversion, if the probe input voltage is greater than the threshold threshold, it is logic "1", otherwise it is logic "0"; The conversion chip converts level logic into LVDS (Low Voltage Differential Signal, low voltage differential signal), so that FPGA can accurately receive channel data. The system software running the logic analyzer in th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More