NAND flash memory structure logic MTP compatible with CMOS technology

A flash memory and process technology, applied in the field of integrated circuits, can solve problems such as high process cost, long R&D cycle, and incompatibility of CMOS logic process, and achieve the effect of reducing bit area and cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The present invention will be further described below in conjunction with drawings and embodiments.

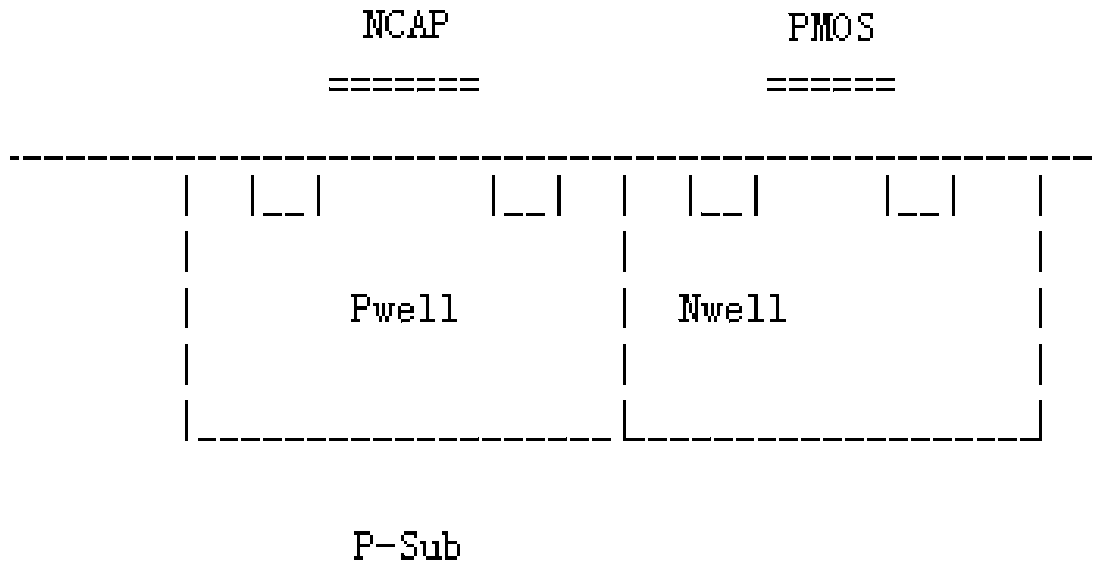

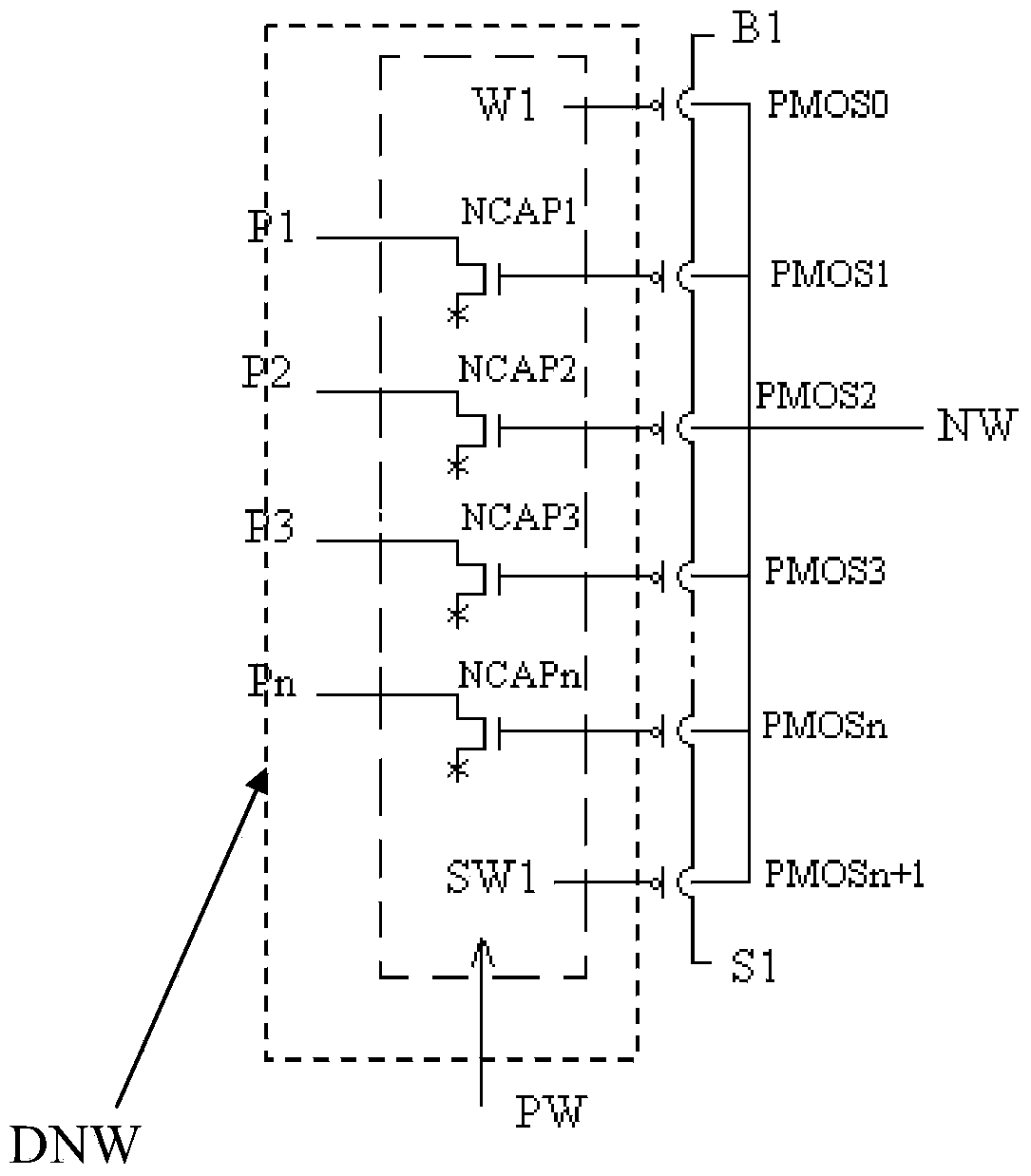

[0014] The logical MTP of the NAND flash memory structure of the present invention comprises: a PMOS transistor and an NCAP (NMOS is done in the N well) capacitance composition unit, wherein the NCAP capacitance has a floating gate, the drain of the NCAP capacitance is connected to the programming line, and the NCAP capacitance The floating gate is connected to the gate of the PMOS transistor; as figure 1 NCAP1 and PMOS1 constitute units in NCAP2 and PMOS2 constitute units, and so on. The drains of the NCAP capacitors NCAP1 , NCAP2 , . . . , NCAPn are respectively connected to programming lines P1 , P2 , . . . Pn. Then 2 or more such cells are combined in series, that is, the drain of each PMOS transistor is connected to the source of the next PMOS transistor, such as figure 1 PMOS1, PMOS2, . . . , PMOSn connected in series. The source of the first PMOS transistor PM...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com