Array substrate, manufacturing method thereof, and display device

A technology of array substrates and substrate substrates, which is applied in semiconductor/solid-state device manufacturing, optics, instruments, etc., can solve problems affecting product yield and achieve the effect of avoiding ESD phenomena

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

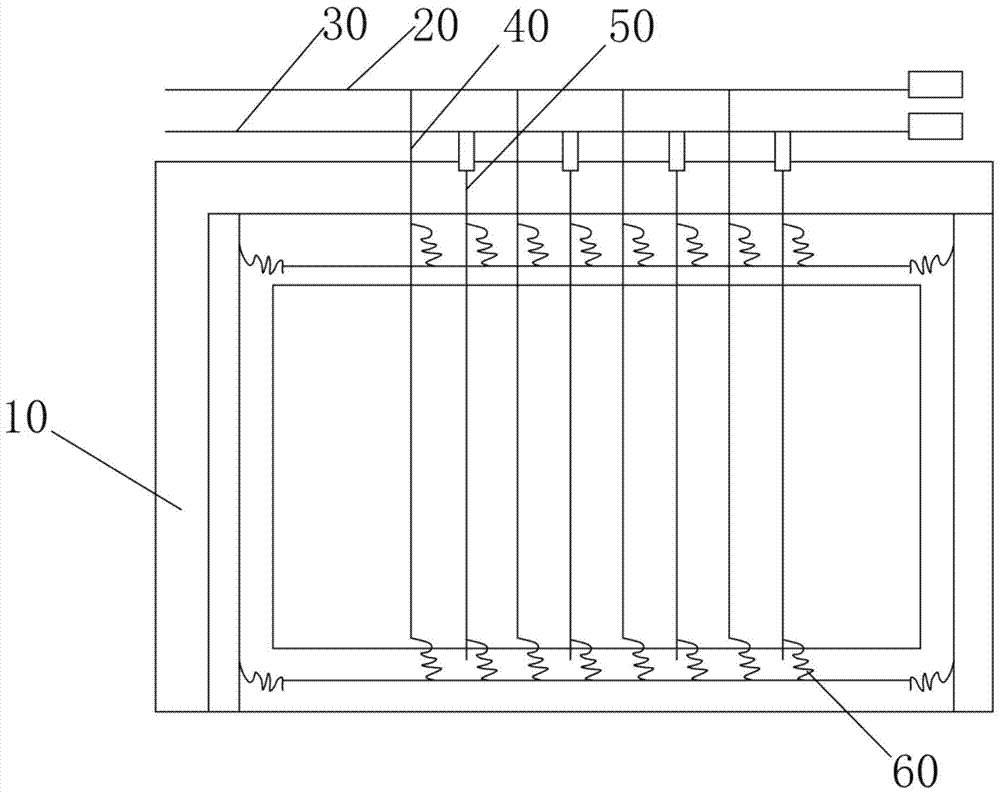

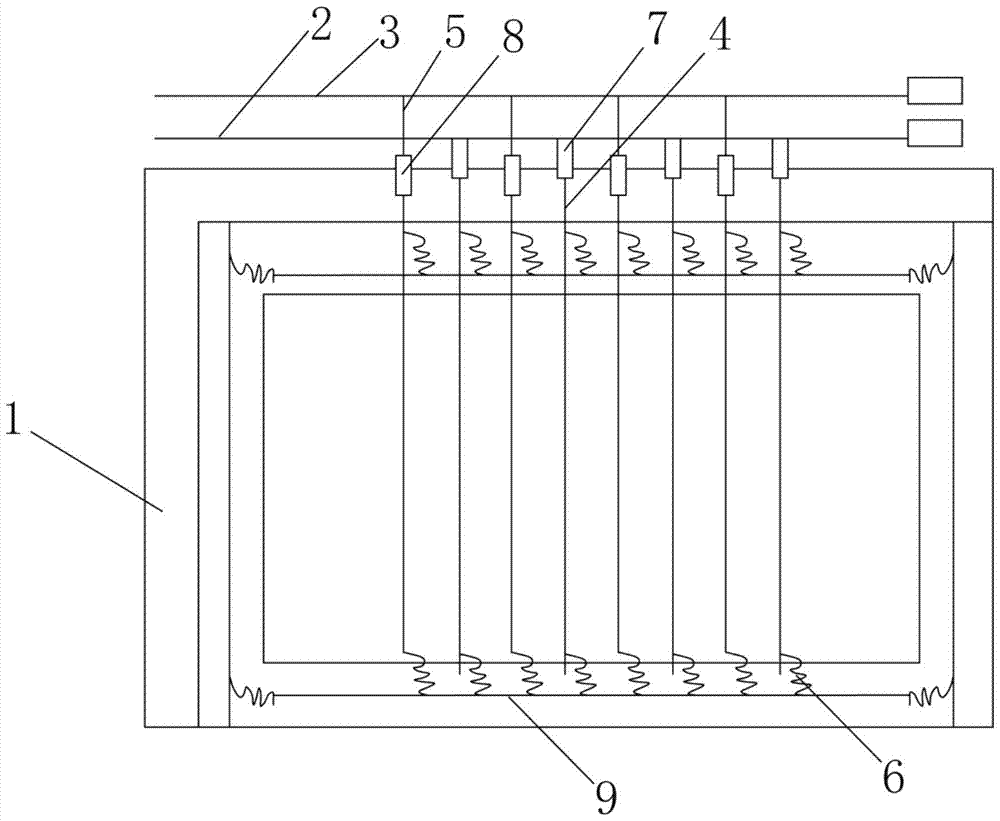

[0032] For the convenience of testing, in the TFT-LCD manufacturing process, it is necessary to check the wiring on the array substrate. Therefore, in order to facilitate the wiring inspection, the data lines of the array substrate are generally divided into two groups of odd and even, and each group is connected to a different short circuit, such as figure 2 As shown, an array substrate of the present invention includes a base substrate 1, a first short circuit 2, a first insulating layer, a data line and a second insulating layer sequentially formed on the base substrate 1 from bottom to top. , the layer where the data line is located is formed with a second short-circu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More